## In the Matter of

# CERTAIN CONSUMER ELECTRONICS AND DISPLAY DEVICES WITH GRAPHICS PROCESSING AND GRAPHICS PROCESSING UNITS THEREIN

337-TA-932

Publication 4903 June 2019

# U.S. International Trade Commission

Washington, DC 20436

# U.S. International Trade Commission

#### **COMMISSIONERS**

Meredith Broadbent, Chairman Dean Pinkert, Vice Chairman Irving Williamson, Commissioner David Johanson, Commissioner Scott Kieff, Commissioner Rhonda Schmidtlein, Commissioner

Address all communications to Secretary to the Commission United States International Trade Commission Washington, DC 20436

# **U.S. International Trade Commission**

Washington, DC 20436 www.usitc.gov

### In the Matter of

# CERTAIN CONSUMER ELECTRONICS AND DISPLAY DEVICES WITH GRAPHICS PROCESSING AND GRAPHICS PROCESSING UNITS THEREIN

337-TA-932

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN CONSUMER ELECTRONICS AND DISPLAY DEVICES WITH GRAPHICS PROCESSING AND GRAPHICS PROCESSING UNITS THEREIN

Investigation No. 337-TA-932

# NOTICE OF COMMISSION DECISION NOT TO REVIEW THE ALJ'S FINAL INITIAL DETERMINATION FINDING NO VIOLATION OF SECTION 337; TERMINATION OF INVESTIGATION

**AGENCY**: U.S. International Trade Commission.

**ACTION**: Notice.

**SUMMARY**: Notice is hereby given that the U.S. International Trade Commission has determined not to review the final initial determination (ID) issued on October 9, 2015, which found no violation of section 337 of the Tariff Act of 1930, 19 U.S.C. § 1337, in this investigation.

FOR FURTHER INFORMATION CONTACT: Ron Traud, Office of the General Counsel, U.S. International Trade Commission, 500 E Street, S.W., Washington, D.C. 20436, telephone (202) 205-3427. Copies of non-confidential documents filed in connection with this investigation are or will be available for inspection during official business hours (8:45 a.m. to 5:15 p.m.) in the Office of the Secretary, U.S. International Trade Commission, 500 E Street, S.W., Washington, D.C. 20436, telephone (202) 205-2000. General information concerning the Commission may also be obtained by accessing its Internet server at <a href="http://www.usitc.gov">http://www.usitc.gov</a>. The public record for this investigation may be viewed on the Commission's electronic docket (EDIS) at <a href="http://edis.usitc.gov">http://edis.usitc.gov</a>. Hearing-impaired persons are advised that information on this matter can be obtained by contacting the Commission's TDD terminal on (202) 205-1810.

**SUPPLEMENTARY INFORMATION:** The Commission instituted this investigation based on a complaint filed by NVIDIA Corporation of Santa Clara, California (NVIDIA). The investigation was instituted to determine whether there is a violation of subsection (a)(1)(B) of section 337 in the importation into the United States, the sale for importation, or the sale within the United States after importation of certain consumer electronics and display devices with graphics processing and graphics processing units therein by reason of infringement of one or more of

The authority for the Commission's determination is contained in section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337), and in sections 210.42-46 of the Commission's Rules of Practice and Procedure (19 C.F.R. §§ 210.42-46).

By order of the Commission.

Lisa R. Barton

Secretary to the Commission

Issued: December 14, 2015

# CERTAIN CONSUMER ELECTRONICS AND DISPLAY DEVICES WITH GRAPHICS PROCESSING AND GRAPHICS PROCESSING UNITS THEREIN

#### **PUBLIC CERTIFICATE OF SERVICE**

I, Lisa R. Barton, hereby certify that the attached **NOTICE** has been served by hand upon the Commission Investigative Attorney, R. Whitney Winston, Esq., and the following parties as indicated, on **December 14, 2015.**

Lisa R. Barton, Secretary U.S. International Trade Commission 500 E Street, SW, Room 112 Washington, DC 20436

#### On Behalf of Complainant NVIDIA Corporation: I. Neel Chatterjee ☐ Via Hand Delivery ORRICK, HERRINGTON & SUTCLIFFE LLP ☐ Via Express Delivery 1000 Marsh Road ☑ Via First Class Mail Menlo Park, California 94025 $\square$ Other: On Behalf of Respondent Qualcomm, Inc.: Deanna Tanner Okun, Esq. ☐ Via Hand Delivery ADDUCI, MASTRIANI & SCHAUMBERG LLP ☐ Via Express Delivery 1133 Connecticut Ave., NW, 12th Floor ☑ Via First Class Mail Washington, DC 20036 ☐ Other: On Behalf of Samsung Electronics Co., Ltd., Samsung Telecommunications America, LLC, and Samsung Semiconductor, Inc.: D. Sean Trainor, Esq. ☐ Via Hand Delivery KIRKLAND & ELLIS LLP ☐ Via Express Delivery 655 Fifteenth Street, NW ⊠ Via First Class Mail Washington, DC 20005 ☐ Other:

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN CONSUMER ELECTRONICS AND DISPLAY DEVICES WITH GRAPHICS PROCESSING AND GRAPHICS PROCESSING UNITS THEREIN

Inv. No. 337-TA-932

#### **INITIAL DETERMINATION ON VIOLATION OF SECTION 337**

Administrative Law Judge Thomas B. Pender

(October 09, 2015)

Pursuant to the Notice of Investigation and Rule 210.42(a) of the Rules of Practice and Procedure of the United States International Trade Commission, this is my Initial Determination in the matter of Certain Consumer Electronics And Display Devices With Graphics Processing And Graphics Processing Units Therein, Investigation No. 337-TA-932.

# Table of Contents

| I.   | INT  | RODUCTION                                                 |    |

|------|------|-----------------------------------------------------------|----|

|      | A.   | The Parties                                               | 3  |

|      |      | 1. Complainant                                            | 3  |

|      |      | 2. Respondents                                            | 3  |

|      | B.   | Products at Issue                                         | 4  |

| II.  | JUR  | ISDICTION                                                 | 6  |

|      | A.   | Subject Matter Jurisdiction                               |    |

|      | B.   | Personal Jurisdiction                                     |    |

|      | C.   | In Rem Jurisdiction                                       | 7  |

| III. | REL  | EVANT LAW                                                 | 7  |

|      | A.   | Infringement                                              | 7  |

|      |      | 1. Claim Construction                                     | 7  |

|      |      | 2. Direct Infringement                                    | 8  |

|      |      | a. Literal Infringement                                   | 8  |

|      |      | b. Doctrine of Equivalents                                | 9  |

|      |      | 3. Indirect Infringement                                  |    |

|      | B.   | Invalidity                                                |    |

|      |      | 1. Anticipation                                           | 11 |

|      |      | 2. Obviousness                                            |    |

|      |      | 3. Written Description and Enablement                     |    |

|      | C.   | Domestic Industry – Technical Prong                       |    |

| IV.  | U.S. | PATENT NO. 7,209,140                                      |    |

|      | A.   | Level of Ordinary Skill in the Art                        |    |

|      | B.   | Claim Construction                                        | 17 |

|      |      | 1. Order No. 20: Construing Terms of the Asserted Patents |    |

|      |      | 2. Agreed Construction - "programmable by the user"       |    |

|      |      | 3. Disputed Constructions                                 |    |

|      |      | a. "graphics data"/"operations on the graphics data"      | ,  |

|      |      | b. "hardware graphics accelerator"                        |    |

|      | ·    | c. "reciprocal instruction"                               |    |

|      | C.   | Infringement                                              |    |

|      | D.   | Domestic Industry – Technical Prong                       |    |

|      | E.   | Invalidity                                                | 38 |

| •   |        | 1.           | Anticipation – 35 U.S.C. 102                                                                                    | 38   |

|-----|--------|--------------|-----------------------------------------------------------------------------------------------------------------|------|

|     |        | 2.           | Obviousness – 35 U.S.C. 103                                                                                     | 43   |

|     |        |              | a. Renderman on Horizon860                                                                                      | 43   |

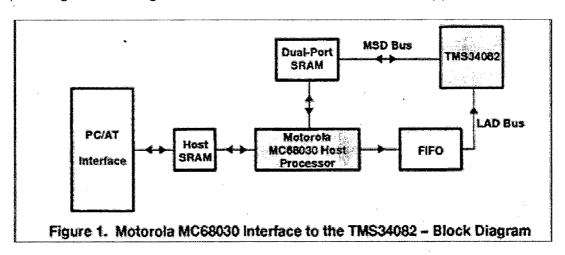

|     |        |              | b. "C" Language on TMS34082                                                                                     | 45   |

|     |        | 3.           | Inventorship – 35 U.S.C. 102(f)                                                                                 | 52   |

| V.  | U.S. P | ATEN]        | Γ NO. 6,690,372                                                                                                 | 59   |

| **  | A      | Level        | of Ordinary Skill in the Art                                                                                    | 60   |

|     | B.     | Claim        | Construction                                                                                                    | 60   |

|     |        | 1.           | Order No. 20: Construing Terms of the Patent - "shading calculation"                                            | 60   |

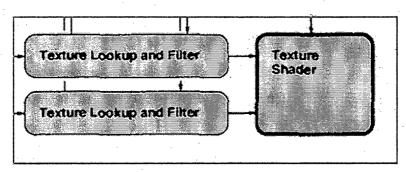

|     |        | 2.<br>(Claim | Disputed Term - "texture look-up module coupled to the shading module 23)                                       |      |

|     | C.     | Infring      | gement                                                                                                          | 71   |

|     |        | 1.           | Claim 23                                                                                                        | 71   |

|     |        |              | a. Sufficiency of NVIDIA's infringement evidence                                                                | . 72 |

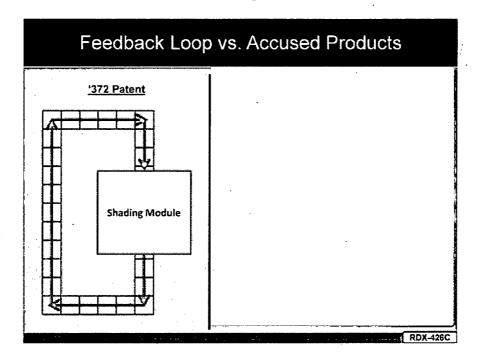

|     |        | •            | b. Do the Accused Products have a "shading module" and a "textur look-up module" coupled to a "shading module"? |      |

| •   |        |              | c. Conclusion                                                                                                   | 81   |

|     |        | 2.           | Claim 24                                                                                                        |      |

|     | D.     |              | stic Industry – Technical Prong                                                                                 |      |

|     | E.     | Invalid      | lity                                                                                                            | 87   |

|     |        | 1.           | Anticipation                                                                                                    | 87   |

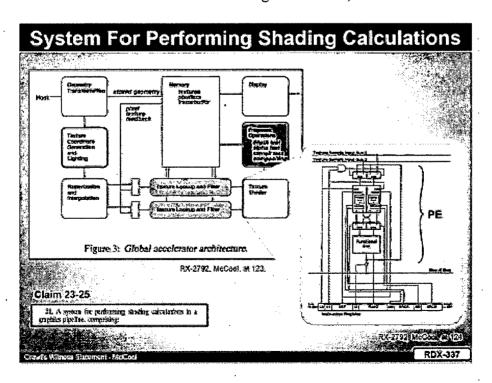

|     |        |              | a. "McCool"                                                                                                     | . 87 |

|     |        |              | b. U.S. Patent No. 6,236,413                                                                                    | 101  |

|     |        |              | c. "Ackerman"                                                                                                   | 108  |

|     |        | 2.           | Obviousness                                                                                                     | 114  |

| VI. | U.S. P | ATENT        | Γ NO. 7,038,6851                                                                                                | 114  |

|     | A.     | Level        | of Ordinary Skill in the Art1                                                                                   | 115  |

|     | В.     | Claim        | Construction                                                                                                    | 117  |

|     |        | 1.           | Agreed construction - "dynamically controlling"                                                                 | 117  |

|     |        | 2.           | Disputed construction - "graphics processor"                                                                    | 117  |

|     | ·C.    | Infring      | gement                                                                                                          | 123  |

|     |        | 1.           | Claim 1                                                                                                         |      |

|     |        |              | a. Mali GPUs                                                                                                    | 123  |

|     |        |              | b. Adreno GPUs                                                                                                  |      |

|     |        | 2            | ·                                                                                                               | 137  |

|       |       |        | a.        | Mali GPUs                                           | 137 |

|-------|-------|--------|-----------|-----------------------------------------------------|-----|

| -     |       |        | b.        | Adreno GPUs                                         | 137 |

| -     | D.    | Dom    | estic Inc | dustry - Technical Prong                            | 138 |

|       | E     | Inval  | idity     |                                                     | 138 |

| .* .  |       | 1.     | Antic     | cipation (35 U.S.C. § 102) – The ATI Unified Shader | 138 |

|       |       |        | a.        | Conception                                          | 140 |

|       |       |        | b.        | Reduction to Practice                               | 145 |

|       |       |        | c.        | Conclusion                                          | 149 |

|       |       | 2.     | Obvi      | ousness – 35 U.S.C. 103                             | 149 |

|       |       |        |           | Selzer in view of Van Hook                          |     |

|       |       |        | b.        | Amanatides in view of Van Hook                      | 160 |

| VII.  | DOM   | IESTIC | INDUS     | STRY                                                | 162 |

| VIII. | CON   | CLUSI  | ONS O     | F LAW                                               | 164 |

| IX.   | INITI | IAL DE | ETERM     | INATION AND ORDER                                   | 165 |

#### **Table of Abbreviations**

| CDX  | Complainant's Demonstrative Exhibit                                    |

|------|------------------------------------------------------------------------|

| CIB  | Complainant's Initial Post-Hearing Brief                               |

| CRB  | Complainant's Reply Post-Hearing Brief                                 |

| CX   | Complainant's Exhibit                                                  |

| Dep. | Deposition                                                             |

| JX   | Joint Exhibit                                                          |

| RDX  | Respondent's Demonstrative Exhibit                                     |

| RIB  | Respondent's Initial Post-Hearing Brief                                |

| RRB  | Respondent's Reply Post-Hearing Brief                                  |

| RX   | Respondent's Exhibit                                                   |

| Tr.  | Transcript                                                             |

| DWS  | Direct Witness Statement (Including Revised Direct Witness Statements) |

| RWS  | Rebuttal Witness Statement                                             |

#### I. INTRODUCTION

Complainant NVIDIA Corporation ("NVIDIA") filed a complaint on September 4, 2014 alleging a violation of Section 337 based on infringement of seven patents: (i) U.S. Patent No. 6,198,488 ("the '488 patent"); (ii) U.S. Patent No. 6,992,667 ("the '667 patent"); (iii) U.S. Patent No. 7,209,140 ("the '140 patent"); (iv) U.S. Patent No. 6,690,372 ("the '372 patent"); (v) U.S. Patent No. 7,038,685 ("the '685 patent"); (vi) U.S. Patent No. 7,015,913 ("the '913 patent"); and (vii) U.S. Patent No. 6,697,063 ("the '063 patent"). (Compl. ¶ 5). On October 10, 2014, the Commission instituted an investigation, by publication of a notice in the *Federal Register*, to determine:

whether there is a violation of subsection (a)(1)(B) of section 337 in the importation into the United States, the sale for importation, or the sale within the United States after importation of certain consumer electronics and display devices with graphics processing and graphics processing units therein by reason of infringement of one or more of claims 1, 19, and 20 of the '488 patent; claims 1-29 of the '667 patent; claims 1-5, 7-19, 21-23, 25-30, 34-36, 38, 41-43 of the '685 patent; claims 5-8, 10, 12-20 and 24-27 of the '913 patent; claims 7, 8, 11-13, 16-21, 23, 24, 28, and 29 of the '063 patent; claims 1-10, 12, and 14 of the '140 patent; and claims 1-6, 9-16, and 19-25 of the '372 patent, and whether an industry in the United States exists as required by subsection (a)(2) of section 337....

79 Fed. Reg. 61338 (Oct. 10, 2014).

A *Markman* hearing was held on February 2 and 3, 2015, and an order construing the disputed terms issued on April 2, 2015. (Order No. 20 (Apr. 2, 2015) ("*Markman* Order")). In addition, the Commission has determined that NVIDIA satisfies the economic prong of the domestic industry requirement with respect to each of the asserted patents. (Notice of Commission Determination not to Review an Initial Determination Granting Complainants' Unopposed Motion for Summary Determination that the Economic Prong of the Domestic Industry Requirement is Satisfied (Apr. 22, 2015).)

NVIDIA filed four motions for partial termination based on its withdrawal of certain allegations set forth in its complaint. On December 31, 2014, NVIDIA filed a motion seeking termination with respect to claim 19 of the '488 patent. (Mot. Docket Nos. 932-013). The motion was granted, and the investigation was terminated with respect to that claim on February 18, 2015. (*See* Order No. 10 (Jan. 15, 2015); Notice (Feb. 18, 2015)). On June 8, 2015, June 22, 2015, and June 25, 2015, NVIDIA filed motions seeking termination with respect to the '488 patent, the '667 patent, the '913 patent, the '063 patent, and claims 4, 16, 19, and 21 of the '685 patent. (Mot. Docket No. 932-047, 932-051, 932-060). These motions were granted and the investigation was terminated with respect to these claims and patents. (*See* Order No. 35.)

The following patent assertions remain: claim 14 of the '140 patent; claims 23 and 24 of the '372 patent; and claims 1 and 15 of the '685 patent (respectively, the "Asserted Claims" and the "Asserted Patents").

#### A. The Parties

#### 1. Complainant

Complainant NVIDIA Corporation ("NVIDIA") is a Delaware corporation having a principal place of business in Santa Clara, California. (Complaint at ¶ 12).

#### 2. Respondents

Respondent Samsung Electronics Co., Ltd. is a corporation organized under the laws of South Korea having a principal place of business at Samsung Main Building, 250 Taepyung-ro 2-ka, Chung-ku, Seoul 100-742, Korea. (Samsung Answer at ¶ 25). Samsung Electronics Co., Ltd. manufactures the accused mobile phones and tablet computers at issue in this investigation. Respondent Samsung Telecommunications America, LLC is a Delaware limited liability company having a principal place of business at 1301 Lookout Drive, Richardson, Texas 75802. (Id. at ¶ 28.) Samsung Telecommunications America, LLC is involved in the importation and sale in the United States after importation of the accused mobile phones and tablet computers at issue in this investigation. (Id.) Respondent Samsung Semiconductor, Inc. is a California corporation having a principal place of business at 3655 North First Street, San Jose, California 95134. (Id. at ¶ 29.) Respondent Samsung Electronics America, Inc. is a New York corporation having a principal place of business at 85 Challenger Road, Ridgefield Park, New Jersey 07660. (Id. at ¶ 27.) Samsung Electronics America, Inc. is a wholly-owned subsidiary of Samsung Electronics Co., Ltd. (Id. at ¶ 27.) Samsung Telecommunications America, LLC and Samsung Semiconductor, Inc. are subsidiaries of Samsung Electronics America, Inc. (*Id.* at ¶¶ 28-29.) Samsung Electronics Co., Ltd., Samsung Telecommunications America, LLC, Samsung

Semiconductor, Inc., and Samsung Electronics America, Inc. are referred to collectively herein as "Samsung."

Respondent Qualcomm, Inc. ("Qualcomm") is a Delaware corporation having a principal place of business at 5775 Morehouse Drive, San Diego, California 92121. (Qualcomm Answer at ¶ 23). Qualcomm designs, has-manufactured, and sells mobile processors with Adreno graphics processing units ("GPU") that are used in certain accused Samsung devices. (*Id.*)

#### B. Products at Issue

The parties still disagree about what products are actually at issue in this investigation. (CRB at 3; RRB at 4-6.) It is black letter law that the scope of a Section 337 investigation is determined by the Commission's Notice of Investigation ("NOI"). Thus, in determining what products are at issue in this investigation, I must turn to the NOI to see how the Commission defined the scope of this investigation.

The scope of this investigation is defined in the NOI as "certain consumer electronics and display devices with graphics processing and graphics processing units therein." 79 Fed. Reg. 61338 (Oct. 10, 2014). NVIDIA argues that the NOI defines the scope as: (1) certain consumer electronics and display devices with graphics processing; and (2) graphics processing units therein. Respondents and the Staff maintains the scope of the investigation is certain consumer electronics and display devices with graphics processing and graphics processing units therein (*i.e.*, "with graphics processing and graphics processing units therein" is a single prepositional phrase that modifies "certain consumer electronics and display devices.").

The syntax of the NOI only supports the position of the Respondents and the Staff. If the phrase "graphics processing units therein" was meant to be a separate clause from "certain consumer electronics and display devices with graphics processing" there would be a comma

after "...with graphics processing." Without such a comma, the phrase "with graphics processing and graphics processing units therein" reads as a single prepositional phrase.

Moreover, NVIDIA's argument is belied by the following table from its own opening posthearing brief.

| Patent    | Claim | Accused Products                                             |

|-----------|-------|--------------------------------------------------------------|

| 6 600 272 | 23    | Samsung consumer products with Adreno, Mali, or PowerVR GPUs |

| 6,690,372 | 24    | Samsung consumer products with Mali GPUs                     |

| 7,209,140 | 14    | Samsung consumer products with Adreno, Mali, or PowerVR GPUs |

| 7.029.695 | 1     | Samsung consumer products with Adreno or Mali GPUs           |

| 7,038,685 | 15    | Samsung consumer products with Adreno or Mali GPUs           |

(CIB at 2.) The above table makes clear the Accused Products are "Samsung consumer products ..." NVIDIA does not identify any GPU, by itself, as an Accused Product and certainly Qualcomm's GPUs are not Samsung consumer products. Accordingly, for at least the reasons above, I find the scope of this investigation is limited to consumer electronics and display devices that include graphics processing capabilities and that have graphics processing units therein.

Consistent with the NOI, the Accused Products in this investigation are Samsung mobile devices, including phones and tablets, that employ one of the following five GPU architectures: (i) Qualcomm Adreno A3X (302, 305, 306, 320, 330); (ii) Qualcomm Adreno A4X (420, 430); (iii) ARM Mali T-6X (604, 624, 628); (iv) ARM Mali T-7X (720, 760); and (v) Imagination PowerVR SGX 5X (540, 544). (CIB at 2.)

For purposes of the domestic industry requirement, NVIDIA relies upon its GPUs with Kepler, Fermi, and Maxwell architectures (*i.e.*, GeForce Titan Z, GeForce GTX750 TI, and Tegra K1 processors) and products incorporating those GPUs. (CIB at 23, 63, 129.)

#### II. JURISDICTION

In order to have the power to decide a case, a court or agency must have both subject matter jurisdiction and jurisdiction over either the parties or the property involved. 19 U.S.C. § 1337; *Certain Steel Rod Treating Apparatus and Components Thereof*, Inv. No. 337-TA-97, Commission Memorandum Opinion, 215 U.S.P.Q. 229, 231 (1981).

#### A. Subject Matter Jurisdiction

Section 337 confers subject matter jurisdiction on the International Trade Commission to investigate, and if appropriate, to provide a remedy for, unfair acts and unfair methods of competition in the importation, the sale for importation, or the sale after importation of articles into the United States. (See 19 U.S.C. §§ 1337(a)(1)(B) and (a)(2).) NVIDIA alleges in the Complaint a violation of Subsection 337(a)(1)(B) in the importation and sale of products that infringe the Asserted Patents. (See Complaint.) NVIDIA has alleged sufficient facts that, if proven, would show Samsung and Qualcomm imported articles that infringe NVIDIA's patents. See Certain Elec. Devices with Image Processing Sys., Components Thereof, & Assoc. Software, Inv. No. 337-TA-724, Comm'n Op. at 8-10 (Dec. 2, 2011) (citing Amgen, Inc. v. ITC, 902 F.2d 1532, 1536 (Fed. Cir. 1990)). Accordingly, I find the Commission has subject matter jurisdiction over this Investigation under Section 337 of the Tariff Act of 1930

#### B. Personal Jurisdiction

Respondents Samsung and Qualcomm have appeared and fully participated in this investigation by, among other things, participating in discovery, participating in the evidentiary hearing, and filing pre-hearing and post-hearing briefs. Accordingly, I find Respondents Samsung and Qualcomm have submitted to the jurisdiction of the Commission. *See Certain Miniature Hacksaws*, Inv. No. 337-TA-237, Pub. No. 1948, Initial Determination at 4, 1986 WL 379287 (U.S.I.T.C., October 15, 1986) (unreviewed by Commission in relevant part).

#### C. In Rem Jurisdiction

Samsung has stipulated to importation of the Accused Products and further stipulated it does not and will not dispute the importation requirement within the meaning of 19 USC § 1337(a)(1)(B) is satisfied in this Investigation. (See JX-020C.) See Certain Kinesiotherapy Devices, Inv. No. 337-TA-823, ID, at 11-12 (Jan. 8, 2013) (unreviewed in relevant part) citing Amgen, Inc. v. U.S. Int'l Trade Comm'n, 902 F.2d 1532, 1536 (Fed. Cir. 1990).

Qualcomm denies engaging in any importation-related activities with respect to the Accused Products, but does not contest that the Accused Products (*i.e.*, the Samsung mobile devices at issue in this investigation) have been imported, as stipulated to by Samsung. Thus, I find the Accused Products have been imported into the United States. Accordingly, the Commission has *in rem* jurisdiction over the Accused Products. *See Sealed Air Corp. v. United States Int'l Trade Comm'n*, 645 F.2d 976, 985 (C.C.P.A. 1981).

#### III. RELEVANT LAW

#### A. Infringement

"An infringement analysis entails two steps. The first step is determining the meaning and scope of the patent claims asserted to be infringed. The second step is comparing the properly construed claims to the device accused of infringing." *Markman v. Westview Instruments, Inc.*, 52 F.3d 967, 976 (Fed. Cir. 1995) (*en banc*) (internal citations omitted), *aff'd*, 517 U.S. 370 (1996).

#### 1. Claim Construction

"Claim construction is generally a matter of law ... but it may have underlying factual determinations." Summit 6, LLC v. Samsung Electronics Co., Ltd., 2015 WL 5515331 (Fed. Cir. 2015) (citing Teva Pharm. USA, Inc. v. Sandoz, Inc., —U.S. —, —, 135 S.Ct. 831, 837, — L.Ed.2d —, — (2015). "The construction of claims is simply a way of elaborating the

normally terse claim language in order to understand and explain, but not to change, the scope of the claims." *Embrex, Inc. v. Serv. Eng'g Corp.*, 216 F.3d 1343, 1347 (Fed. Cir. 2000).

Claim construction focuses on the intrinsic evidence, which consists of the claims themselves, the specification, and the prosecution history. See Phillips v. AWH Corp., 415 F.3d 1303, 1314 (Fed. Cir. 2005) (en banc); see also Markman, 52 F.3d at 979. As the Federal Circuit in Phillips explained, courts must analyze each of these components to determine the "ordinary and customary meaning of a claim term" as understood by a person of ordinary skill in art at the time of the invention. 415 F.3d at 1313. "Such intrinsic evidence is the most significant source of the legally operative meaning of disputed claim language." Bell Atl. Network Servs., Inc. v. Covad Commc'ns Grp., Inc., 262 F.3d 1258, 1267 (Fed. Cir. 2001). When the intrinsic evidence does not establish the meaning of a claim, then extrinsic evidence (i.e., all evidence external to the patent and the prosecution history, including dictionaries, inventor testimony, expert testimony, and learned treatises) may be considered. Phillips, 415 F.3d at 1317.

#### 2. Direct Infringement

A complainant must prove either literal infringement or infringement under the doctrine of equivalents. Infringement must be proven by a preponderance of the evidence. *SmithKline Diagnostics, Inc. v. Helena Labs. Corp.*, 859 F.2d 878, 889 (Fed. Cir. 1988). A preponderance of the evidence standard "requires proving that infringement was more likely than not to have occurred." *Warner-Lambert Co. v. Teva Pharm. USA, Inc.*, 418 F.3d 1326, 1341 n.15 (Fed. Cir. 2005).

#### a. Literal Infringement

Literal infringement is a question of fact. *Finisar Corp. v. DirecTV Group, Inc.*, 523 F.3d 1323, 1332 (Fed. Cir. 2008). Literal infringement requires the patentee to prove that the accused device contains each and every limitation of the asserted claim(s). *Frank's Casing Crew &*

Rental Tools, Inc. v. Weatherford Int'l, Inc., 389 F.3d 1370, 1378 (Fed. Cir. 2004). If any claim limitation is absent, there is no literal infringement of that claim as a matter of law. Bayer AG v. Elan Pharm. Research Corp., 212 F.3d 1241, 1247 (Fed. Cir. 2000).

#### b. Doctrine of Equivalents

Where literal infringement is not found, infringement nevertheless can be found under the doctrine of equivalents. Determining infringement under the doctrine of equivalents "requires an intensely factual inquiry." *Vehicular Techs. Corp. v. Titan Wheel Int'l, Inc.*, 212 F.3d 1377, 1381 (Fed. Cir. 2000). According to the Federal Circuit:

Infringement under the doctrine of equivalents may be found when the accused device contains an "insubstantial" change from the claimed invention. Whether equivalency exists may be determined based on the "insubstantial differences" test or based on the "triple identity" test, namely, whether the element of the accused device "performs substantially the same function in substantially the same way to obtain the same result." The essential inquiry is whether "the accused product or process contain elements identical or equivalent to each claimed element of the patented invention[.]"

TIP Sys., LLC v. Phillips & Brooks/Gladwin, Inc., 529 F.3d 1364, 1376-77 (Fed. Cir. 2008) (citations omitted). Thus, if an element is missing or not satisfied, infringement cannot be found under the doctrine of equivalents as a matter of law. London v. Carson Pirie Scott & Co., 946 F.2d 1534, 1538-39 (Fed. Cir. 1991).

#### 3. Indirect Infringement

Section 271(b) of the Patent Act prohibits inducement: "[w]hoever actively induces infringement of a patent shall be liable as an infringer." 35 U.S.C. § 271(b). See DSU Med. Corp. v. JMS Co., 471 F.3d 1293, 1305 (Fed. Cir. 2006) (en banc) ("To establish liability under section 271(b), a patent holder must prove that once the defendants knew of the patent, they actively and knowingly aid[ed] and abett[ed] another's direct infringement.")

Section 271(c) of the Patent Act prohibits contributory infringement: "Under 35 U.S.C. § 271(c), a party who sells a component with knowledge that the component is especially designed for use in a patented invention, and is not a staple article of commerce suitable for substantial noninfringing use, is liable as a contributory infringer." *Wordtech Sys., Inc. v. Integrated Networks Solutions, Inc.*, 609 F.3d 1308, 1316 (Fed. Cir. 2010).

#### B. Invalidity

It is Respondents' burden to prove invalidity, and the burden of proof never shifts to the patentee to prove validity. *Scanner Techs. Corp. v. ICOS Vision Sys. Corp. N.V.*, 528 F.3d 1365, 1380 (Fed. Cir. 2008). "Under the patent statutes, a patent enjoys a presumption of validity, *see* 35 U.S.C. § 282, which can be overcome only through facts supported by clear and convincing evidence[.]" *SRAM Corp. v. AD-II Eng'g, Inc.*, 465 F.3d 1351, 1357 (Fed. Cir. 2006).

The clear and convincing evidence standard placed on the party asserting the invalidity defense requires a level of proof beyond the preponderance of the evidence. Although not susceptible to precise definition, "clear and convincing" evidence has been described as evidence which produces in the mind of the trier of fact "an abiding conviction that the truth of a factual contention is 'highly probable.'" *Price v. Symsek*, 988 F.2d 1187, 1191 (Fed. Cir. 1993) (citing *Buildex, Inc. v. Kason Indus., Inc.*, 849 F.2d 1461, 1463 (Fed. Cir. 1988).)

"When no prior art other than that which was considered by the PTO examiner is relied on by the attacker, he has the added burden of overcoming the deference that is due to a qualified government agency presumed to have properly done its job[.]" *Am. Hoist & Derrick Co. v. Sowa & Sons, Inc.*, 725 F.2d 1350, 1359 (Fed. Cir. 1984). Therefore, the challenger's "burden is especially difficult when the prior art was before the PTO examiner during prosecution of the

application." Hewlett-Packard Co. v. Bausch & Lomb Inc., 909 F.2d 1464, 1467 (Fed. Cir. 1990).

#### 1. Anticipation

Under 35 U.S.C. § 102(a), a patent is invalid for anticipation if it was "patented, described in a printed publication, or in public use, on sale, or otherwise available to the public before the effective filing date of the claimed invention." 35 U.S.C. § 102(a). The Federal Circuit has held that "[a] patent is invalid for anticipation if a single prior art reference discloses each and every limitation of the claimed invention. Moreover, a prior art reference may anticipate without disclosing a feature of the claimed invention if that missing characteristic is necessarily present, or inherent, in the single anticipating reference." Schering Corp. v. Geneva Pharm., Inc., 339 F.3d 1373, 1377 (Fed. Cir. 2003) (citations omitted). "Inherency, however, may not be established by probabilities or possibilities. The mere fact that a certain thing may result from a given set of circumstances is not sufficient." Continental Can Company USA v. Monsanto Company, 948 F.2d 1264, 1269 (Fed. Cir. 1991). To be considered anticipatory, a prior art reference must describe the applicant's "claimed invention sufficiently to have placed it in possession of a person of ordinary skill in the field of the invention." Helifix Ltd. v. Blok-Lok, Ltd., 208 F.3d 1339, 1346 (Fed. Cir. 2000) (quoting In re Paulsen, 30 F.3d 1475, 1479 (Fed. Cir. 1994)). Anticipation is a question of fact. Texas Instruments, Inc. v. U.S. Int'l Trade Comm'n, 988 F.2d 1165, 1177 (Fed. Cir. 1993).

#### 2. Obviousness

Under 35 U.S.C. § 103(a), a patent is valid unless "the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would

<sup>&</sup>lt;sup>1</sup> For patent applications filed before March 16, 2013, the relevant priority date is "before the invention thereof by the applicant for a patent." See MPEP § 2131.

have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains." 35 U.S.C. § 103(a). The ultimate question of obviousness is a question of law, but "it is well understood that there are factual issues underlying the ultimate obviousness decision." *Richardson-Vicks Inc. v. Upjohn Co.*, 122 F.3d 1476, 1479 (Fed. Cir. 1997); *Wang Lab., Inc. v. Toshiba Corp.*, 993 F.2d 858, 863 (Fed. Cir. 1993). The underlying factual determinations include: (1) the scope and content of the prior art, (2) the level of ordinary skill in the art, (3) the differences between the claimed invention and the prior art, and (4) objective indicia of non-obviousness. *Graham v. John Deere Co.*, 383 U.S. 1, 17 (1966).

Although the Federal Circuit has historically required that, in order to prove obviousness, the patent challenger must demonstrate, by clear and convincing evidence, that there is a "teaching, suggestion, or motivation to combine," the Supreme Court has rejected this "rigid approach." *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 417-418 (2007). In *KSR*, the Supreme Court described a more flexible analysis:

Often, it will be necessary for a court to look to interrelated teachings of multiple patents; the effects of demands known to the design community or present in the marketplace; and the background knowledge possessed by a person having ordinary skill in the art, all in order to determine whether there was an apparent reason to combine the known elements in the fashion claimed by the patent at issue... As our precedents make clear, however, the analysis need not seek out precise teachings directed to the specific subject matter of the challenged claim, for a court can take account of the inferences and creative steps that a person of ordinary skill in the art would employ.

Id. Since KSR was decided, the Federal Circuit has announced that, where a patent challenger contends that a patent is invalid for obviousness based on a combination of prior art references, "the burden falls on the patent challenger to show by clear and convincing evidence that a person of ordinary skill in the art would have had reason to attempt to make the composition or

device, . . . and would have had a reasonable expectation of success in doing so." *PharmaStem Therapeutics, Inc. v. Viacell, Inc.*, 491 F.3d 1342, 1360 (Fed. Cir. 2007).

#### 3. Written Description and Enablement

35 U.S.C. § 112 is the basis for the written description and enablement requirements:

The specification shall contain a written description of the invention, and the manner and process of making and using it, in such full, clear, concise, and exact terms as to enable any person skilled in the art to which it pertains, or with which it is most nearly connected, to make and use the same ...

35 U.S.C. § 112, ¶ 1.

The hallmark of the written description requirement is the disclosure of the invention.

Ariad Pharm., Inc. v. Eli Lilly and Co., 598 F.3d 1336, 1351 (Fed. Cir. 2010) (en banc). The test for determining the sufficiency of the written description in a patent requires "an objective inquiry into the four comers of the specification from the perspective of a person of ordinary skill in the art. Based on that inquiry, the specification must describe an invention understandable to that skilled artisan and show that the inventor actually invented the invention claimed." Id.

Compliance with the written description requirement is a question of fact and "the level of detail required to satisfy the written description requirement varies depending on the nature and scope of the claims and on the complexity and predictability of the relevant technology." Id.

"To be enabling, the specification of a patent must teach those skilled in the art how to make and use the full scope of the claimed invention without 'undue experimentation."

Genentech, Inc. v. Novo Nordisk, A/S, 108 F.3d 1361, 1365 (Fed.Cir.1997) (quoting In re Wright, 999 F.2d 1557, 1561 (Fed. Cir. 1993)). Enablement serves the dual function in the patent system of ensuring adequate disclosure of the claimed invention and of preventing claims broader than the disclosed invention. MagSil Corp. v. Hitachi Global Storage Technologies, Inc., 687 F.3d 1377, 1380 -1381 (Fed. Cir. 2012). "The scope of the claims must be less than or equal to the

scope of the enablement to ensure that the public knowledge is enriched by the patent specification to a degree at least commensurate with the scope of the claims." *Sitrick v. Dreamworks*, LLC, 516 F.3d 993, 999 (Fed. Cir. 2008) (quoting *Nat'l Recovery Techs., Inc. v. Magnetic Separation Sys., Inc.*, 166 F.3d 1190, 1195-96 (Fed. Cir. 1999). The enablement determination proceeds as of the effective filing date of the patent. *Plant Genetic Sys., N.V. v. DeKalb Genetics Corp.*, 315 F.3d 1335, 1339 (Fed. Cir. 2003).

#### C. Domestic Industry – Technical Prong

In a patent-based complaint, a violation of Section 337 can be found "only if an industry in the United States, relating to the articles protected by the patent ... concerned, exists or is in the process of being established." 19 U.S.C. § 1337(a)(2). Under Commission precedent, this "domestic industry requirement" of section 337 consists of an economic prong and a technical prong. *Certain Stringed Musical Instruments and Components Thereof*, Inv. No. 337-TA-586, Comm'n Op. at 12-14 (May 16, 2008). The complainant bears the burden of establishing that the domestic industry requirement is satisfied. *See Certain Set-Top Boxes and Components Thereof*, Inv. No. 337-TA-454, Initial Determination at 294 (June 21, 2002) (unreviewed by Commission in relevant part).

The technical prong of the domestic industry requirement is satisfied when the complainant in a patent-based section 337 investigation establishes that it is practicing or exploiting the patents at issue. See 19 U.S.C. §1337 (a)(2) and (3); Certain Microsphere Adhesives, Process for Making Same and Prods. Containing Same, Including Self-Stick Repositionable Notes, Inv. No. 337-TA-366, Comm'n Op. at 8 (Jan. 16, 1996). "In order to satisfy the technical prong of the domestic industry requirement, it is sufficient to show that the domestic industry practices any claim of that patent, not necessarily an asserted claim of that

patent." Certain Ammonium Octamolybdate Isomers, Inv. No. 337-TA-477, Comm'n Op. at 55 (August 28, 2003).

The test for claim coverage for the purposes of the technical prong of the domestic industry requirement is the same as that for infringement. *Certain Doxorubicin and Preparations Containing Same*, Inv. No. 337-TA-300, Initial Determination at 109, (May 21, 1990), *aff'd*, Views of the Commission at 22 (October 31, 1990); *Alloc, Inc. v. Int'l Trade Comm'n*, 342 F.3d 1361, 1375 (Fed. Cir. 2003). "First, the claims of the patent are construed. Second, the complainant's article or process is examined to determine whether it falls within the scope of the claims." Inv. No. 337-TA-300, Initial Determination at 109. To prevail, the patentee must establish by a preponderance of the evidence that the domestic product practices one or more claims of the patent. The technical prong of the domestic industry can be satisfied either literally or under the doctrine of equivalents. *Certain Dynamic Sequential Gradient Devices and Component Parts Thereof*, Inv. No. 337-TA-335, Initial Determination at 44, Pub. No. 2575 (May 15, 1992).

#### IV. U.S. PATENT NO. 7,209,140

U.S. Patent No. 7,209,140 ("the '140 patent") is titled "System, Method and Article of Manufacture for a Programmable Vertex Processing Model With Instruction Set." (JX-006, '140 patent). The '140 patent issued on April 24, 2007, and lists John Erik Lindholm, David B. Kirk, Henry P. Moreton, and Simon Moy as inventors. (*Id.*). The '140 patent has five figures and 14 claims. (*Id.*). Independent claims 1, 5-7, 12, and 14, and dependent claims 2-4 and 8-10 were asserted in this investigation. *See* 79 Fed. Reg. 61338 (Oct. 10, 2014) ("Notice of Investigation"). However, only claim 14 of the '140 patent remains at issue in this investigation. (CIB at 2; Tr. at 14:17-20; CX-006C (Aliaga) at Q&A 21).

The '140 patent generally relates to hardware accelerated computer graphics. (*See* '140 patent at 1:17-19, 51-55). According to the '140 patent:

Graphics application program interfaces (API's) have been instrumental in allowing applications to be written to a standard interface and to be run on multiple platforms, i.e. operating systems. Examples of such API's include Open Graphics Library (OpenGL®) and D3D<sup>TM</sup> transform and lighting pipelines. OpenGL® is the computer industry's standard graphics API for defining 2-D and 3-D graphic images. With OpenGL®, an application can create the same effects in any operating system using any OpenGL®-adhering graphics adapter. OpenGL® specifies a set of commands or immediately executed functions. Each command directs a drawing action or causes special effects.

(JX-006 at 1:23-34). One of the benefits of standardized APIs, such as OpenGL and D3D, is the ability to optimize the available commands using hardware graphics accelerators. (*Id.* at 1:43-47). However, standardized APIs were slow to change. (*Id.* at 1:43-50). Accordingly, the '140 patent asserts that there was "a need to provide a new computer graphics programming model and instruction set that allows convenient implementation of changes to the graphics API, while preserving the driver and hardware optimization afforded by currently established graphics API's." (*Id.* at 1:57-61).

To that end, the '140 patent proposes a programmable hardware graphics accelerator that provides "instructions from a predetermined instruction set" to make various operations available to programmers. (*Id.* at 1:65-2:4).

NVIDIA alleges infringement of claim 14 of the '140 patent, which reads as follows with emphasis added to indicate disputed and construed terms:

#### Claim 14. A system, comprising:

- a central processing unit; and

- a hardware graphics accelerator for receiving graphics data, and performing programmable operations on the graphics data in order to generate output;

wherein the operations are programmable by a user utilizing instructions from a predetermined instruction set capable of being executed by the hardware graphics accelerator, the predetermined instruction set including a reciprocal instruction, a reciprocal square root instruction, a three component dot product instruction, a four component dot product instruction, a distance instruction, a minimum instruction, a maximum instruction, an exponential instruction, and a logarithm instruction.

(JX-006 at 24:23-38.)

#### A. Level of Ordinary Skill in the Art

In Order No. 20, I found that a person of ordinary skill in the art of the '140 patent would have "at least a four-year degree in Electrical Engineering, Computer Engineering, Computer Science, or equivalent, as well as at least two years of experience in graphics processing including developing, designing or programming software or hardware for graphics processing units, hardware graphics accelerators or other graphics processing systems." (Markman Order at 18 (April 2, 2015); CIB at 18, 58; RIB at 117.)

#### B. Claim Construction

#### 1. Order No. 20: Construing Terms of the Asserted Patents

With respect to claim 14 of the '140 patent, I construed the following terms:

| Claim Language                                 | Construction (Order No. 20)                     |

|------------------------------------------------|-------------------------------------------------|

| "operation"                                    | "an action or process recognized by the         |

|                                                | hardware graphics accelerator"                  |

| "instructions from a predetermined instruction | "the complete set of instructions recognized by |

| set"                                           | a given computer or provided by a given         |

| ·                                              | programming language"                           |

(Markman Order at 25, 32.)

#### 2. Agreed Construction - "programmable by the user"

The parties agree that the term "programmable by the user" should be construed to mean "an application writer can create graphics functionality by causing instructions from a predetermined instruction set to be executed." (CIB at 45; RIB at 12-13; SIB at 14.)

#### 3. Disputed Constructions

#### a. "graphics data"/"operations on the graphics data"

The parties dispute the meaning of the phrases "graphics data" and "operations on the graphics data" in claim 14 of the '140 patent. (CIB at 51-54; RIB at 13-14, SIB at 14-15.)

| Term                        | Proposed Constructions                          |                                         |                                         |  |

|-----------------------------|-------------------------------------------------|-----------------------------------------|-----------------------------------------|--|

| refin                       | Complainant                                     | Respondents                             | Staff                                   |  |

| "graphics data"             | data used in vertex processing                  | data related to graphics                | data related to graphics                |  |

| "operations on the graphics | operations during vertex processing of graphics | No construction necessary. See          | No construction necessary. See          |  |

| data"                       | data                                            | "operations" and "graphics data" above. | "operations" and "graphics data" above. |  |

#### **The Parties' Positions**

NVIDIA argues that its proposed constructions of "graphics data" and "operations on the graphics data" properly define the scope of the claimed invention. (CIB at 51.) NVIDIA asserts the '140 Patent is directed to the vertex processing portion of the graphics pipeline. (*Id.*) NVIDIA argues its constructions reflect this and focus on operations performed (and data used) during the vertex processing. Specifically, NVIDIA argues its construction of "graphics data" is correct because it covers both types of data used during vertex processing (*e.g.*, constant and/or vertex data as disclosed in the '140 Patent), and excludes data used only in portions of the pipeline that are not subject of the '140 Patent, (*e.g.*, pixel data). (*Id.* at 51-52.)

NVIDIA argues Respondents' proposal construction of "graphics data" as any "data related to graphics" would broaden the claims to cover operations performed in portions of the graphics pipeline not contemplated by the '140 Patent. (*Id.* at 52.)

NVIDIA argues that Respondents' construction ignores the legal requirement that the term be construed in the context of the intrinsic evidence (e.g., the claims, specification, and file history). (Id.) According to NVIDIA, "Where the specification makes clear at various points

that the claimed invention is narrower than the claim language might imply, it is entirely permissible and proper to limit the claims." (*Id.* (citing *Alloc, Inc. v. ITC*, 342 F.3d 1361, 1370 (Fed. Cir. 2003).) NVIDIA argues the specification consistently describes "the present invention" as enabling a user to "program a portion of the graphics pipeline that handles vertex processing." (*Id.*) NVIDIA also asserts that the specification distinguishes between "the programmable vertex processing of the present invention" and the "remaining portions of the graphics pipeline" that are not part of the invention. (*Id.* at 53.) NVIDIA argues that every embodiment in the '140 patent is directed to the vertex processing portion of the graphics pipeline and performing operations on data used in vertex processing, specifically constant and/or vertex data. (*Id.*) NVIDIA argues nothing in the patent suggests the invention is directed to another portion of the graphics pipeline. (*Id.*) Thus, NVIDIA argues that because the '140 Patent specification repeatedly and consistently describes the "present invention" as a whole as directed to programmable vertex processing, and only discloses embodiments directed to the same, its construction is proper and should be adopted. (*Id.* at 54.)

Respondents argue that NVIDIA improperly seeks to limit the scope of claim 14 by construing the term "graphics data" to include only one type of graphics data—graphics data used in vertex processing. (RIB at 13.) Respondents argue the intrinsic evidence places no such limitation on the term. (*Id.*) Respondents argue the term "graphics data" should be construed in accordance with its plain meaning: "data related to graphics." (*Id.* at 14.) Likewise, Respondents argue the plain meaning of "operations on the graphics data" is "operations" on that same data. (*Id.*) Respondents assert that NVIDIA's expert, Dr. Aliaga, confirmed that the plain meaning of "graphics data" is not limited to vertex data but includes, for example, pixel data. (*Id.*) Respondents argue that the intrinsic evidence also supports its construction noting that the

Field of Invention states "the invention relates to computer graphics" in general and dependent claims 2 and 8 separately limit graphics data to vertex data. (Id.)

The Staff argues that the plain and ordinary meaning of the term "graphics data" is simply "data related to graphics." (SIB at 15.) The Staff argues this construction is consistent with the claim language and with the specification. (Id.) The Staff argues NVIDIA seeks a narrower construction that would import a limitation from the specification to narrowly construe "graphics data" as "data used in vertex processing." (Id.). Such a construction, the Staff asserts, is improper in the absence of an expression of intent by the patentee. (Id. (citing Phillips, 415 F.3d at 1323; Vitronics, 90 F.3d at 1582-83; Markman, 52 F.3d at 979-80; Intel Corp. v. U.S. International Trade Commission, 946 F.2d at 836 ("Where a specification does not require a limitation, that limitation should not be read from the specification into the claims.").) The Staff argues neither the plain language of the claim nor the specification of the '140 patent evidence an intent by the patentee to limit the term "graphics data" beyond its plain and ordinary meaning. (Id.) Thus, according to the Staff, NVIDIA's proposed construction should be rejected and the term "graphics data" should be construed as "data related to graphics." (Id.) With regard to the phrase "operations on the graphics data," the Staff argues this phrase need not be construed in light of the constructions of "operations" and "graphics data." (Id.)

#### **Discussion**

The term "graphics data" is used only in the claims of the '140 patent. There is no recitation of the term in the specification. The Federal Circuit has stated that "[i]n some cases, the ordinary meaning of claim language as understood by a person of skill in the art may be readily apparent even to lay judges." *Phillips v. AWH Corp.*, 415 F.3d 1303, 1314 (Fed. Cir. 2005). Here, the term "graphics data" is broad and its meaning self-explanatory. "Graphics

data" is data related to graphics. This interpretation is consistent with the term's plain and ordinary meaning as understood by one of ordinary skill in the art. (RX-005C (Diefendorff) at Q&A 92, 96.) This interpretation is also consistent with the claims and specification of the '140 patent. (*Id.* at Q&A 94.)

NVIDIA seeks to narrowly construe "graphics data" as "data used in vertex processing." NVIDIA argues that term "graphics data" should be read to exclude certain types of graphics data, such as pixel data, based on its disavowal of claim scope. (*See* CIB at 51-54.) Specifically, NVIDIA contends that claim 14 of the '140 patent should be limited to programmable vertex processing for two reasons. First, NVIDIA argues that the specification of the '140 patent repeatedly and consistently describes the invention as a whole as requiring programmable vertex processing. (*Id.* at 54.) Second, NVIDIA argues that the '140 patent only discloses embodiments that provide programmable vertex processing. (*Id.*) For the reasons set forth below, the evidence does not support NVIDIA's position.

NVIDIA relies on portions of the specification that refer to "vertex processing" or "programmable vertex processing" for the proposition that the claimed invention should be limited to only programmable vertex processing. (*See* CIB at 52-53.) The cited evidence, however, does not demonstrate clear and unmistakable disclaimer, as is necessary to depart from the usual and customary meaning. *Thorner*, 669 F.3d at 1366-67 ("To constitute disclaimer, there must be a clear and unmistakable disclaimer."). Although the preferred embodiments describe programmable vertex processing, not programmable primitive processing, nothing in the patent precludes programmable primitive processing. Indeed, the '140 patent even contemplates alternative embodiments that enable programmable primitive processing. (JX-006 at 4:1-14 ("the programmable graphics mode may also supersede the standard graphics API

during primitive processing").) Moreover, the language of the claims suggests NVIDIA's construction cannot be correct. Independent claims 1 and 7 both recite "graphics data," while dependent claims 2 and 8 state that graphics data "includes vertex data." This claim language implies the term graphics data is broader than just vertex data.

Also, contrary to NVIDIA's argument, the '140 patent does not repeatedly and consistently require programmable vertex processing. For example, the "Field of Invention" states broadly that the "present invention relates to computer graphics, and more particularly to providing programmability in a computer graphics processing pipeline." (JX-006 at 1:15-19.) The evidence shows vertex processing is just one part of the graphics pipeline. (RX-005C (Diefendorff) at Q&A 94.) Likewise, the "Description of the Invention" describes the invention without reference to vertex processing:

A system, method and article of manufacture are provided for programmable processing in a computer graphics pipe line. Initially, data is received from a source buffer. Thereafter, programmable operations are performed on the data in order to generate output. The operations are programmable in that a user may utilize instructions from a predetermined instruction set for generating the same. Such output is stored in a register. During operation, the output stored in the register is used in performing the programmable operations on the data.

(JX-006 at 1:65-2:7.) The Abstract of the '140 patent similarly describes the invention broadly without limiting the claimed invention to vertex processing. (*Id.*, Abstract).

Nothing in the intrinsic record indicates the applicant acted as his own lexicographer by assigning a special meaning to the term "graphics data" and nothing in the specification or prosecution history shows the applicant clearly and unmistakably disavowed claim scope. Thus, I find no reason to depart from the term's plain and ordinary meaning. Such meaning, as discussed above, is also consistent with the language of the claims and specification.

Accordingly, I find for at least the reasons above, that one of ordinary skill in the art at the time of the invention would have construed the term "graphics data" as "data related to graphics."

In light of my construction of "graphics data" as "data related to graphics" I find it unnecessary to further construe the phrase "operations on graphics data."

#### b. "hardware graphics accelerator"

The parties dispute the meaning of the phrase "hardware graphics accelerator" in claim 14 of the '140 patent. (CIB at 47-51; RIB at 14-17.)

| Tr           | Proposed Constructions |                          |                          |  |

|--------------|------------------------|--------------------------|--------------------------|--|

| Term         | Complainant            | Respondents              | Staff                    |  |

| "hardware    | "graphics processing   | plain and ordinary       | plain and ordinary       |  |

| graphics     | unit (GPU)"            | meaning - "hardware      | meaning – "hardware      |  |

| accelerator" |                        | for processing graphics" | for processing graphics" |  |

#### The Parties' Positions

NVIDIA asserts that the dispute regarding this term centers on whether a "hardware graphics accelerator" requires a hardware implementation of the graphics pipeline, *i.e.*, a GPU, or whether it can be construed to encompass general-purpose processors programmed to process graphics data. (CIB at 47-48.) NVIDIA argues the intrinsic record of the patent makes clear the term does not include general-purpose processors. (*Id.* at 48.) NVIDIA asserts that one of ordinary skill understands the '140 Patent uses "hardware graphics accelerator" to refer to a hardware implementation of a graphics pipeline, *i.e.*, a GPU. (*Id.*) NVIDIA argues that the claims distinguish between hardware graphics accelerators and CPUs and that claim 14 separately recites both. (*Id.*) NVIDIA argues that the patent specification also distinguishes between hardware graphic accelerators and CPUs. (*Id.*) NVIDIA argues the "Background of the Invention" makes clear that specialized chips having a hardware implementation of the graphics

pipeline are central to the invention. (*Id.*) NVIDIA asserts that the '140 patent explains how the prior art approach of implementing the graphics pipeline in specialized hardware afforded benefits in terms of acceleration but suffered from a lack of flexibility due to its fixed-function nature. (*Id.*) NVIDIA asserts that the '140 patent solved this problem by adding programmability to the vertex processing portion of a specialized graphics chip, which is the claimed invention of the '140 patent. (*Id.* at 49.) NVIDIA argues that the inventors confirmed the '140 patent was directed at specialized hardware and not general-purpose processors such as CPUs. (*Id.*)

NVIDIA maintains the discussion in the '140 patent about adding programmability to graphics chips only makes sense as a description of hardware graphics accelerators as NVIDIA construes the term (*i.e.*, a hardware implementation of a graphics pipeline), because general-purpose processors are inherently programmable. (*Id.*) NVIDIA alleges that during prosecution, the applicants and the Examiner agreed that general-purpose processor art was not analogous to the claimed hardware graphics accelerators. (*Id.* at 49-50.) NVIDIA asserts that to overcome a prior art general-purpose processor, applicants amended the claims to repeatedly recite a "hardware graphics accelerator." (*Id.* at 50.)

NVIDIA contends Respondents ignore the specification, file history and other evidence to offer a construction that captures general purpose processors. (*Id.*) NVIDIA argues that according to Respondents, a general-purpose processor is a "hardware graphics accelerator" if used to process graphics, but not if used for a different purpose. (*Id.* at 51.) NVIDIA argues one of ordinary skill would understand that whether something is a "hardware graphics accelerator" is determined by its structure and not its use. (*Id.*) NVIDIA argues that Respondents reliance on the conclusory assertion of their expert, Mr. Diefendorff, to show that hardware graphics

accelerators encompass general purpose processors must be rejected as inconsistent with the intrinsic evidence. (*Id.*)

Respondents argue that both the intrinsic evidence and their expert, Mr. Diefendorff, confirm that the term "hardware graphics accelerator" ("HGA") should be given its plain and ordinary meaning as "hardware for processing graphics data." (RIB at 14.) Respondents argue that the '140 patent does not ascribe any special meaning to the term, instead stating that it can take on "various configuration[s]." (*Id.* at 15.) Respondents argue that despite conceding that the term "HGA" should be given its plain and ordinary meaning, NVIDIA improperly limits the term to a "graphics processing unit" with specialized, fixed-function circuitry for rasterization and texturing. (*Id.*) But, Respondents argue, the '140 patent never mentions a "GPU," a "rasterizer," or "special" texture hardware, and NVIDIA cannot cite any intrinsic support. (*Id.*) Respondents assert that one of the named '140 inventors conceded that such fixed-function hardware is not needed to perform the claimed instructions. (*Id.*)

Respondents argue NVIDIA's reliance on the prosecution history in support of its proposed construction is misplaced. (*Id.* at 15-16.) Respondents assert the prosecution history never defines or explains the meaning of "hardware graphics accelerator" and that despite the claims being rejected three times, NVIDIA only mentioned HGA once, to contrast the instructions from an "archaic" general processor that never mentioned graphics with those of a hardware graphics accelerator. (*Id.* at 16.) Respondents argue that during prosecution, NVIDIA never mentioned a GPU, fixed-function hardware, a rasterizer, or a texture unit. (*Id.*) Respondents argue that while claim 14 mentions both a CPU and an HGA, it does not limit the meaning of HGA as NVIDIA contends nor does it support NVIDIA's construction. (*Id.*) Respondents also argue that NVIDIA's alleged plain and ordinary meaning of "hardware

graphics accelerator" fails to account for the term's actual usage in the field many years before NVIDIA's coined the term "GPU." (*Id.*)

The Staff argues the term should be given its plain and ordinary meaning, which is simply "hardware for processing graphics." (SIB at 16.) The Staff argues this construction is consistent with the claim language and with the specification. (Id.). The Staff argues that NVIDIA improperly seeks a narrower construction that would limit the claimed "hardware graphics accelerator" to a GPU. (*Id.*)

#### Discussion

The evidence shows the plain and ordinary meaning of the term "hardware graphics accelerator" is simply "hardware for processing graphics." (RX-005C (Diefendorff) at Q&A 86-91; RX-3497C (Diefendorff) at Q&A 23; see also RX-3494C (Yu) at Q&A 20-30).) This construction is consistent with the claim language, specification, and prosecution history. (RX-3497C (Diefendorff) at Q&A 25, 27, 28.) The patent specification does not use the term "hardware graphics accelerator," and only once refers to a "hardware accelerator." There is nothing in the intrinsic record to indicate that the patent applicant assigned this limitation a special meaning or disclaimed part of this limitation's plain and ordinary meaning.

As the name describes, a "hardware graphics accelerator" accelerates the processing of graphics data, which the evidence shows in practice is circuitry that can be implemented in different ways depending on the design needs. (RX-005C (Diefendorff) at Q&A 91.) The evidence shows hardware graphics accelerators can take many forms, including "something as simple as additional hardware added to a CPU or something more complex such as a separate processor." (*Id.* at Q&A 86, 91; RX-3497C (Diefendorff) at Q&A 23.) Contrary to NVIDIA's argument, the evidence shows there were many known programmable processors described in

the art as accelerating graphics processing that do not contain fixed, dedicated hardware. (RX-005C (Diefendorff) at Q&A 90, 91; RX-3497C (Diefendorff) at Q&A 23.)

NVIDIA's main argument in support of its proposed construction is that a hardware graphics accelerator must be different from a CPU because claim 14 separately recites both a hardware graphics accelerator and a CPU, the specification says a hardware graphics accelerator can be implemented in "hardware accelerators of various configuration" or a CPU, and the file history distinguishes a general purpose processor from an hardware graphics accelerator. (CIB at 48-50.) This argument, however, is irrelevant as no party has proposed construing "hardware graphics accelerator" to mean a CPU. (RX-3497C (Diefendorff) at Q&A 28 ("I have not said that a general-purpose CPU, regardless of how it is used in a system, is automatically a hardware graphics accelerator. On the contrary, I have contended only two things: first, that a CPU microprocessor can be employed to function in a system as a hardware graphics accelerator if it is assigned to offloading graphics work from the main CPU, or, second, that a general-purpose CPU microprocessor can be transformed into a hardware graphics accelerator through the addition of new instructions and hardware execution units for the purpose of processing graphics data effectively.").) I find no support in the claim language, specification, or prosecution history of the '140 patent for the limiting construction offered by NVIDIA. (RX-005C (Diefendorff) at Q&A 86-91; (RX-3497C (Diefendorff) at Q&A 25, 27, 28.).) Thus I find NVIDIA's argument in support of its proposed construction not persuasive.

NVIDIA seeks to narrow the plain and ordinary meaning of "hardware graphics accelerator" by construing the term as a separate processor (*i.e.*, a GPU). However, the portions of the intrinsic record relied on by NVIDIA in support of its construction neither define a hardware graphics accelerator nor limit a hardware graphics accelerator to a GPU. In fact, the

terms "graphics processing unit" and "GPU" appear nowhere in the patent or file history of the '140 patent.

With regard to the prosecution history, NVIDIA argues that during prosecution "the applicants and the Examiner agreed that general-purpose processor art was not analogous to the claimed hardware graphics accelerators." (CIB at 49-50.) Specifically, NVIDIA argues that to overcome a rejection based on a prior art general-purpose processor, the applicant stated:

In particular, only applicant teaches and claims "performing programmable operations on the graphics data utilizing the hardware graphics accelerator ...

In particular, applicant emphasizes that, while Deering teaches a graphics system, Struble discloses a general-purpose processor assembler language. ... To simply glean features from the art of general-purpose processor assembler languages and combine the same with the non-analogous art of graphics systems would be improper and frustrate the inventive concepts of applicant, especially in view of the fundamentally different problems which the two arts address.

(CIB at 50 (quoting JX-12.0438-.0448) (emphasis in original).). NVIDIA argues that following this response, the examiner no longer cited references disclosing programming of general-purpose processors. (*Id.*) Contrary to NVIDIA's argument, the applicant never argued that general-purpose processors were non-analogous to the claimed graphics hardware accelerators. Rather, as the quoted text makes clear, the applicant was only arguing that "general-purpose processor assembler languages" were non-analogous to "graphics systems." Moreover, contrary to NVIDIA's assertion, the patent examiner never stated that general-purpose processors were "not analogous." At most, the examiner was silent, and examiner "silence is not a proper basis on which to construe a patent claim." *DeMarini Sports, Inc. v. Worth, Inc.*, 239 F.3d 1314, 1326 (Fed. Cir. 2001).

Accordingly, for at least the reasons above, I find one of ordinary skill in the art at the time of the invention would construe the term "hardware graphics accelerator" to have its plain and ordinary meaning of "hardware for processing graphics."

# c. "reciprocal instruction"

| Term         | Proposed Constructions                   |                  |                  |  |  |

|--------------|------------------------------------------|------------------|------------------|--|--|

| тегш         | Complainant                              | Respondents      | Staff            |  |  |

| "reciprocal  | Plain and ordinary meaning once          | a particular     | a particular     |  |  |

| instruction" | "instruction" is construed.              | instruction that | instruction that |  |  |

| ,            |                                          | inverts a single | inverts a single |  |  |

|              | However, if construed:                   | operand          | operand          |  |  |

|              | "characters used to specify an action or |                  |                  |  |  |

|              | process for calculating a reciprocal"    |                  |                  |  |  |

# The Parties' Positions

NVIDIA argues the term "reciprocal instruction" has a plain and ordinary meaning. (CIB at 46.) NVIDIA argues that a "reciprocal" is a well-known mathematical expression, it is just one divided by x, *i.e.*, 1/x or the "inverse" of x. (*Id.*) Thus, NVIDIA argues, a "reciprocal instruction" is a programming language statement specifying the calculation of a reciprocal. (*Id.*) NVIDIA argues this is consistent with the '140 patent's description of reciprocal. (*Id.*) NVIDIA argues nothing in the '140 patent requires the claimed "reciprocal instruction" to be anything more than an instruction that performs a mathematical reciprocal. (*Id.*) Accordingly, NVIDIA contends "reciprocal instruction" should be construed to mean "characters used to specify an action or process for calculating a reciprocal." (*Id.*)

NVIDIA argues the Respondents and Staff's proposed construction – "a particular instruction that inverts a single operand" – inserts the extraneous and ambiguous words, "particular" and "single." (*Id.*) NVIDIA argues the plain and ordinary meaning does not require such and neither does the 140 patent. (*Id.*) NVIDIA argues the 140 patent teaches broadly that the instruction may be in "any type of programming language" and thus no "particular" format is required. (*Id.*)

NVIDIA contends that Respondents' non-infringement position demonstrates they actually seek an even narrower construction. (*Id.* at 47.) NVIDIA asserts that Respondents' expert, Mr. Diefendorff, bases his non-infringement opinion on a belief that reciprocal instructions must be completely distinct from divide instructions and thus Respondents are really seeking a construction of "reciprocal instruction" that expressly excludes any overlap with a division instruction. (*Id.*) NVIDIA argues the '140 patent contains no such disclaimer. (*Id.*) According to NVIDIA, the '140 Patent never distinguishes reciprocal instructions from divide instructions. (*Id.*) NVIDIA asserts that in fact, divide instructions are never mentioned in the patent or its prosecution history. (*Id.*) Instead, NVIDIA argues the evidence shows that reciprocal is a type of division. (*Id.*) NVIDIA argues Respondents' narrow construction finds no support in the intrinsic evidence or the plain and ordinary meaning of a reciprocal instruction and should be rejected. (*Id.*)

Respondents argue that "reciprocal instruction" means "a particular instruction that inverts a single operand." (RIB at 13.) Respondents argue "reciprocal" modifies "instruction," such that the term is limited to one type of instruction, not a mathematical calculation in the abstract. (*Id.*) Respondents argue a PHOSITA would have understood a "reciprocal instruction" to be monadic, *i.e.*, it receives and operates on a single input or "operand." (*Id.*) Respondents argue this is consistent with the patent's only explanation of the claimed reciprocal instruction. (*Id.*)

Respondents argue that NVIDIA incorrectly rewrites the claimed "reciprocal instruction" to cover a "division" instruction. (*Id.*) However, Respondents argue a PHOSITA would know that a division instruction is different. (*Id.*) Respondents argue that among other things, a division instruction is dyadic, *i.e.*, it receives and operates on two inputs, a numerator and

denominator. (*Id.*) Respondents argue the difference is significant as reciprocal can be easily calculated at significantly greater speed than division. (*Id.*) Respondents also contend there are differences in latency and accuracy, and the prior art consistently distinguished between the two instructions. (*Id.*) Respondents note the '140 patent never mentions a division instruction (Diefendorff, Tr. 960:10-19), and the inventors distinguished between the claimed reciprocal instruction and a division instruction. (*Id.*)

The Staff argues that a division instruction is not the same as a reciprocal instruction. (SIB at 17.) The Staff asserts that division is a dyadic operation, while reciprocal is a monadic operation. (Id.). In addition, the Staff argues reciprocal instructions are more efficient to pipeline because they exhibit constant latency, while division instructions exhibit variable latency and increase complexity. (Id.). The Staff argues one of ordinary skill in the art would not understand a reciprocal instruction to mean a division instruction. (Id.). Thus, the Staff contends the term "reciprocal instruction" should be construed to mean "a particular instruction that inverts a single operand."

# **Discussion**