### In the Matter of

# Certain Integrated Circuits, Chipsets, and Products Containing Same Including Televisions

Investigation No. 337-TA-786

Publication 4406 July 2013

# U.S. International Trade Commission

# **U.S. International Trade Commission**

#### **COMMISSIONERS**

Irving A. Williamson, Chairman Daniel R. Pearson, Commissioner Shara L. Aranoff, Commissioner Dean A. Pinkert, Commissioner David S. Johanson, Commissioner

Address all communications to Secretary to the Commission United States International Trade Commission Washington, DC 20436

## **U.S. International Trade Commission**

Washington, DC 20436 www.usitc.gov

## In the Matter of

# Certain Integrated Circuits, Chipsets, and Products Containing Same Including Televisions

Investigation No. 337-TA-786

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN INTEGRATED CIRCUITS, CHIPSETS, AND PRODUCTS CONTAINING SAME INCLUDING TELEVISIONS **Investigation No. 337-TA-786**

# [CORRECTED] NOTICE OF COMMISSION DECISION TO REVIEW IN PART A FINAL INITIAL DETERMINATION FINDING NO VIOLATION OF SECTION 337; TERMINATION OF INVESTIGATION

**AGENCY**: U.S. International Trade Commission.

**ACTION**: Notice.

**SUMMARY**: Notice is hereby given that the U.S. International Trade Commission has determined to review in part the presiding administrative law judge's ("ALJ") final initial determination ("ID") issued on July 12, 2012, finding no violation of section 337 of the Tariff Act of 1930, 19 U.S.C. § 1337 in the above-captioned investigation. On review, the Commission affirms the ID's finding of no violation, and terminates the investigation.

FOR FURTHER INFORMATION CONTACT: Megan M. Valentine, Office of the General Counsel, U.S. International Trade Commission, 500 E Street, S.W., Washington, D.C. 20436, telephone (202) 708-2301. Copies of non-confidential documents filed in connection with this investigation are or will be available for inspection during official business hours (8:45 a.m. to 5:15 p.m.) in the Office of the Secretary, U.S. International Trade Commission, 500 E Street, S.W., Washington, D.C. 20436, telephone (202) 205-2000. General information concerning the Commission may also be obtained by accessing its Internet server at <a href="http://www.usitc.gov">http://www.usitc.gov</a>. The public record for this investigation may be viewed on the Commission's electronic docket (EDIS) at <a href="http://edis.usitc.gov">http://edis.usitc.gov</a>. Hearing-impaired persons are advised that information on this matter can be obtained by contacting the Commission's TDD terminal on (202) 205-1810.

**SUPPLEMENTARY INFORMATION**: The Commission instituted this investigation on July 14, 2011, based on a complaint filed by Freescale Semiconductor, Inc. of Austin, Texas ("Freescale"). 76 Fed. Reg. 41521-2 (July 14, 2011). The complaint alleges violations of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. § 1337, by reason of infringement of certain claims of U.S. Patent No. 5,467,455 ("the '455 patent"). The complaint further alleges the existence of a domestic industry. The Commission's notice of investigation named Funai Electric Co., Ltd. of Osaka, Japan and Funai Corporation, Inc. of Rutherford, New Jersey (collectively "Funai"); MediaTek Inc. of Hsinchu City, Taiwan ("MediaTek"); and Zoran

Corporation of Sunnyvale, California ("Zoran") as respondents. The Office of Unfair Import Investigations was named as a party. On May 25, 2012, the Commission determined not to review an ID (Order No. 27) terminating the investigation as to Funai on the basis of a consent order. Notice (May 25, 2012). On May 29, 2012, the Commission determined not to review an ID (Order No. 31) terminating the investigation as to certain Zoran products and certain MediaTek products. Notice (May 29, 2012).

On July 12, 2012, the ALJ issued his final ID, finding no violation of section 337 as to the '455 patent. The ID included the ALJ's recommended determination ("RD") on remedy and bonding. In particular, the ALJ found that claims 9 and 10 of the '455 patent are not invalid pursuant to 35 U.S.C. § 102, but that they are invalid pursuant to 35 U.S.C. § 103. The ALJ further found that those Zoran products that were adjudicated in *Integrated Circuits I* are precluded under the doctrine of issue preclusion. The ALJ also found that certain of the accused Zoran products remaining in the investigation infringe claims 9 and 10 of the '455 patent, but that the accused MediaTek products do not infringe claims 9 and 10 of the '455 patent. The ALJ further found that Freescale has failed to satisfy the domestic industry requirement with respect to the '455 patent. The ALJ's RD recommended a limited exclusion order barring entry of Zoran's and MediaTek's infringing integrated circuits, chipsets, and products containing same including televisions. Freescale did not request, and the ALJ did not recommend, issuance of a cease and desist order against Zoran. The ALJ also recommended that respondents be required to post no bond for the importation of products found to infringe during the period of Presidential review.

On July 24, 2012, Freescale filed a petition for review of certain aspects of the final ID's findings concerning infringement, validity, and domestic industry, and preclusion. Also on July 25, 2012, the IA timely filed a petition for review of certain aspect of the final ID's findings concerning claim construction. Further on July 24, 2012, Zoran and MediaTek contingently petitioned for review of certain aspects of the final ID's findings concerning claim construction, infringement, domestic industry, and preclusion. No post-RD statements on the public interest pursuant to Commission Rule 201.50(a)(4) or in response to the post-RD Commission Notice issued on July 16, 2012, were filed. See 77 Fed. Reg. 42764 (July 20, 2012).

Having examined the record of this investigation, including the ALJ's final ID, the petitions for review, and the responses thereto, the Commission has determined to review the final ID in part. Specifically, the Commission has determined to review, and on review, reverses the ALJ's finding that Japanese Patent Application JP H05-83113-A to Kuboki ("Kuboki") discloses the limitation "[a] data processor within an integrated circuit package comprising: . . . a plurality of bus termination circuits" of claim 9 of the '455 patent. The Commission has also determined to review, and on review, affirms with modification the ID's finding that Kuboki in combination with the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent. The Commission has further determined to review the ID's finding that the Kuboki reference in combination with U.S. Patent No. 5,479,123 to Gist ("Gist") renders obvious claims 9 and 10, and on review, finds that the Kuboki reference in combination with Gist and the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent. The Commission has also determined to review the ID's finding that Freescale

failed to establish the existence of a domestic industry based on its licensing activities, and on review, affirms the ID's finding with modification. The Commission has further determined to review the ID's finding that Freescale has failed to show that the Accused Zoran Hybrid Termination Circuits infringe claims 9 and 10 of the '455 patent and on review, affirms the ID's finding with modification.

The Commission has determined not to review the remaining issues decided in the ID. A Commission opinion will issue shortly.

The authority for the Commission's determination is contained in section 337 of the Tariff Act of 1930, as amended (19 U.S.C. § 1337), and in sections 210.42-46 and 210.50 of the Commission's Rules of Practice and Procedure (19 C.F.R. § 210.42-46 and 210.50).

By order of the Commission.

Lisa R. Barton

Acting Secretary to the Commission

Issued: September 13, 2012

# CERTAIN INTEGRATED CIRCUITS, CHIPSETS, AND PRODUCTS CONTAINING SAME INCLUDING TELEVISIONS

337-TA-786

#### **CERTIFICATE OF SERVICE**

I, Lisa R. Barton, hereby certify that the attached **NOTICE** has been served by hand upon Commission Investigative Attorney **Juan S. Cockburn** and the following parties as indicated, on **September 13, 2012**

Lisa R. Barton, Acting Secretary U.S. International Trade Commission 500 E Street, SW Washington, DC 20436

On Behalf of Complainant Freescale Semiconductor, Inc.: Michael Chibib, Esq. ( ) Via Hand Delivery **BRACEWELL & GIULIANI LLP** ( ) Via Overnight Mail 111 Congress Avenue, Suite 2300 (V) Via First Class Mail Austin, TX 78701-4601 ( ) Other: On Behalf of Respondents Funai Electric Co., Ltd. and Funai Corporation, Inc.: Paul Devinsky, Esq. ( ) Via Hand Delivery MCDERMOTT WILL & EMERY LLP ( ) Via Overnight Mail 600 13<sup>th</sup> Street NW, 12<sup>th</sup> Floor (X) Via First Class Mail Washington, DC 20005-3096 ( ) Other: On Behalf of Respondent MediaTek, Inc.: Michael D. Esch, Esq. WILMER CUTLER PICKERING ( ) Via Hand Delivery HALE & DORR LLP ( ) Via Overnight Mail 1875 Pennsylvania Ave., N.W. (X) Via First Class Mail Washington, DC 20006 () Other:

#### On Behalf of Respondent Zoran Corporation:

Mark D. Fowler, Esq. **DLA PIPER LLP (US)**2000 University Avenue

East Palo Alto, CA 94303

| (  | ) | Via Hand Delivery    |

|----|---|----------------------|

| (  | ) | Via Overnight Mail   |

| 4  | 9 | Via First Class Mail |

| (' | ) | Other:               |

# UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN INTEGRATED CIRCUITS, CHIPSETS, AND PRODUCTS CONTAINING SAME INCLUDING TELEVISIONS Investigation No. 337-TA-786

#### **COMMISSION OPINION**

#### I. BACKGROUND

#### A. Procedural History

The Commission instituted this investigation on July 14, 2011, based on a complaint filed by Freescale Semiconductor, Inc. of Austin, Texas ("Freescale"). 76 Fed. Reg. 41521-2 (July 14, 2011). The complaint alleges violations of section 337 of the Tariff Act of 1930, as amended, 19 U.S.C. § 1337 ("section 337"), in the importation into the United States, the sale for importation, and the sale within the United States after importation of certain integrated circuits, chipsets, and products containing same including televisions by reason of infringement of certain claims of U.S. Patent No. 5,467,455 ("the '455 patent"). The complaint further alleges the existence of a domestic industry. The Commission's notice of investigation named Funai Electric Co., Ltd. of Osaka, Japan and Funai Corporation, Inc. of Rutherford, New Jersey (collectively "Funai"); MediaTek Inc. of Hsinchu City, Taiwan ("MediaTek"); and Zoran Corporation of Sunnyvale, California ("Zoran") as respondents. The Office of Unfair Import Investigations was named as

<sup>&</sup>lt;sup>1</sup> Zoran and MediaTek supply integrated circuits, which Freescale accuses of infringing the '455

a party. The Commission later terminated Funai from the investigation on the basis of a consent order. Notice (May 25, 2012).

On July 12, 2012, the presiding administrative law judge ("ALJ") issued his final initial determination ("ID"), finding no violation of section 337 as to the '455 patent. The ID included the ALJ's recommended determination ("RD") on remedy and bonding. On July 24, 2012, Freescale filed a petition for review of certain aspects of the final ID. In particular, as relevant to this opinion, Freescale requested review of the ID's findings that the asserted claims of the '455 patent are obvious, that certain of Zoran's accused products do not infringe that patent, and that Freescale failed to satisfy the domestic industry requirement based on its investments in licensing the '455 patent. Also on July 24, 2012, respondents Zoran and MediaTek each filed contingent petitions for review of certain aspects of the ID. Further on July 25, 2012, the Commission investigative attorney ("IA") timely filed a petition for review of certain aspects of the ID. On August 1, 2012, the parties filed responses to the various petitions. No post-RD statements on the public interest pursuant to Commission Rule 201.50(a)(4) or in response to the post-RD Commission Notice (issued on July 16, 2012) were filed. See 77 Fed. Reg. 42764 (July 20, 2012).

On September 12, 2012, the Commission determined to review the final ID in part, and on review, to affirm the ID's finding of no violation of section 337 and to terminate the investigation. *See* Notice of Commission Decision to Review In Part A Final Initial Determination Finding No Violation of Section 337; Termination of Investigation (Sept. 12,

patent, to Funai for use in the accused Funai downstream products, e.g., televisions, etc. See Complaint at ¶¶50-89.

2012) ("Notice of Review In Part"). As discussed below, the Commission reverses the ALJ's finding that Japanese Patent Application JP H05-83113-A to Kuboki ("Kuboki") discloses the limitation "[a] data processor within an integrated circuit package comprising: . . . a plurality of bus termination circuits" of claim 9 of the '455 patent. The Commission also affirms with modification the ID's finding that Kuboki in combination with the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent. The Commission further finds that the Kuboki reference in combination with U.S. Patent No. 5,479,123 to Gist ("Gist") and the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent. The Commission also affirms with modification the ID's finding that Freescale has failed to show that the Accused Zoran Hybrid Termination Circuits infringe claims 9 and 10 of the '455 patent. The Commission further affirms with modification the ID's finding that Freescale failed to establish the existence of a domestic industry based on its licensing activities.

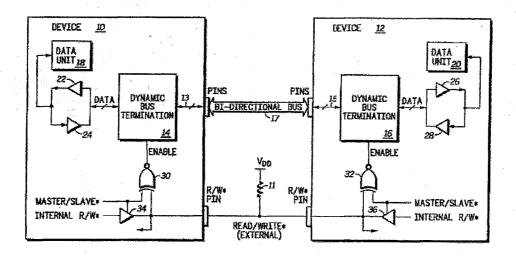

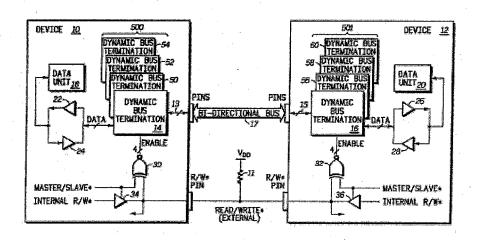

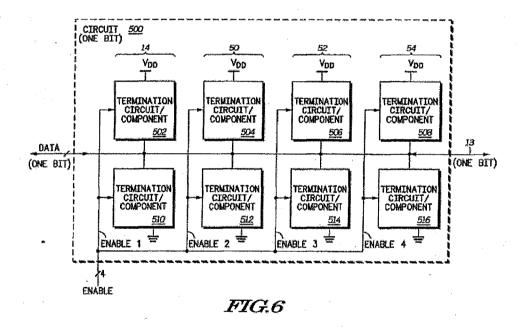

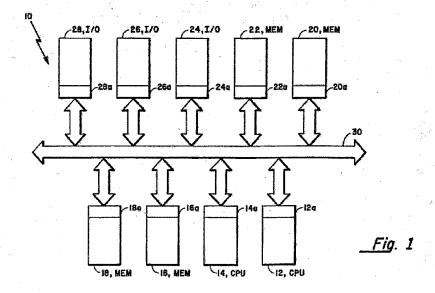

#### B. Patent at Issue

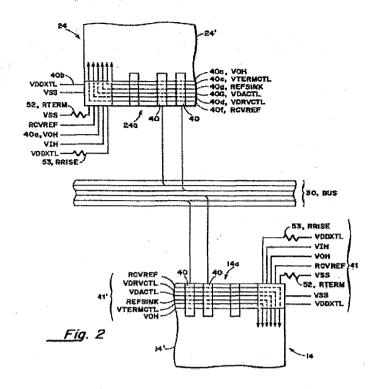

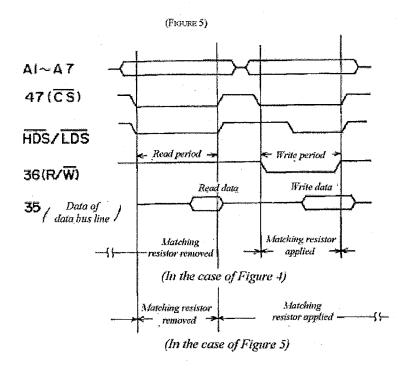

The '455 patent is entitled "Data Processing System and Method for Performing Dynamic Bus Termination," and is directed to a data processor that allows for dynamic termination of conductive bus lines to avoid signal reflection. Signal reflection, or transmission line effect, is a problem that occurs in devices operating at high speeds and/or high clock frequencies, as well as devices that require extremely long conductive interconnections. Signal reflection adversely affects the performance of such devices by increasing the time it takes for a voltage signal to change on the conductor or bus. In general, the claimed invention of the '455 patent allows for dynamic termination at the receiver end of a bi-directional bus to prevent signal reflection in high speed devices. A control signal in the claimed apparatus indicates whether the

device is currently receiving or sending. If the device is sending, the bus termination is enabled to dampen the incoming signal so that no reflections are sent back down the bus (transmission line). When the device is not sending, *e.g.*, receiving, the receiving device's terminators are turned off to reduce the load on the bus and power dissipation of the bus. The patent was originally assigned to Motorola, Inc., which subsequently assigned the patent to Freescale. *See* JX-3; JX-4. The '455 patent has 29 claims, of which claims 9 and 10 are asserted against Zoran and MediaTek.

#### C. Products at Issue

Freescale accused the following MediaTek products of infringing claims 9 and 10 of the '455 patent: [

[] (collectively "the Accused MediaTek Products"). ID at 3, 72.

Freescale accused three groupings of Zoran products of infringing claims 9 and 10 of the '455 patent. Group I consists of [

] (collectively "Accused Zoran Resistor Termination Products"); Group II consists of [

] (where Groups II and II are collectively "Accused Zoran Hybrid Termination Products"). *Id.* The ALJ found that Freescale is precluded under the doctrine of issue preclusion from asserting infringement of claims 9 and 10 of the '455 patent against the following eight Zoran chip models that were specifically adjudicated in a previous investigation involving Freescale and Zoran's products, namely *Certain Integrated Circuits, Chipsets, and Products Containing Same Including Televisions, Media Players, and Cameras*, Inv. No. 337-TA-709 ("*Integrated Circuits P*"): ZR39770BGCF; ZR39772HGCF-B; ZR39775HGCF-B; ZR39775HGCF-C; ZR39775HGCF-TC; ZR39775HGCF-TC-LP; ZR39785HGCF-B; ZR39787HGCF; and ZR39787HGCF-LP. ID at 65.<sup>2</sup> The Commission determined not to review this finding. *See* Notice of Review In Part at 3.

#### II. STANDARD OF REVIEW

Once the Commission determines to review an initial determination, its review is conducted *de novo*. *Certain Polyethylene Terephthalate Yarn and Prods*. *Containing Same*, Inv. No. 337-TA-457, Comm'n Op. at 9 (June 18, 2002). Upon review, the "Commission has 'all the powers which it would have in making the initial determination,' except where the issues are limited on notice or by rule." *Certain Flash Memory Circuits and Prods*. *Containing Same*, Inv. No. 337-TA-382, USITC Pub. 3046, Comm'n Op. at 9-10 (July 1997) (quoting *Certain Acid-Washed Denim Garments and Accessories*, Inv. No. 337-TA-324, Comm'n Op. at 5 (Nov. 1992)). Commission practice in this regard is consistent with the Administrative Procedure Act. *Certain EPROM*, *EEPROM*, *Flash Memory*, *and Flash Microcontroller Semiconductor Devices and*

<sup>&</sup>lt;sup>2</sup> All of the Zoran chips that the ID finds precluded are from Group I of the Zoran Resistor Termination Products.

*Prods. Containing Same,* Inv. No. 337-TA-395, Comm'n Op. at 6 (Dec. 11, 2000) ("*EPROM*"); see also 5 U.S.C. § 557(b).

Upon review, "the Commission may affirm, reverse, modify, set aside or remand for further proceedings, in whole or in part, the initial determination of the administrative law judge. The Commission may also make any findings or conclusions that in its judgment are proper based on the record in the proceeding." 19 C.F.R. § 210.45. This rule reflects the fact that the Commission is not an appellate court, but is the body responsible for making the final agency decision. On appeal, only the Commission's final decision is at issue. *See EPROM* at 6, citing *Fischer & Porter Co. v. U.S. Int'l Trade Comm'n*, 831 F.2d 1574, 1576-77 (Fed. Cir. 1987).

#### III. DISCUSSION

#### A. Obviousness In View Of Kuboki

Under 35 U.S.C. § 103(a), a patent is valid unless "the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains." 35 U.S.C. § 103(a). The ultimate question of obviousness is a question of law, but "it is well understood that there are factual issues underlying the ultimate obviousness decision." *Richardson-Vicks Inc. v. Upjohn Co.*, 122 F.3d 1476, 1479 (Fed. Cir. 1997).

Once claims have been properly construed, "[t]he second step in an obviousness inquiry is to determine whether the claimed invention would have been obvious as a legal matter, based on underlying factual inquiries including: (1) the scope and content of the prior art, (2) the level of ordinary skill in the art, (3) the differences between the claimed invention and the prior art;

and (4) secondary considerations of non-obviousness." *Smiths Indus. Med. Sys., Inc. v. Vital Signs, Inc.*, 183 F.3d 1347, 1354 (Fed. Cir. 1999) (citing *Graham v. John Deere Co.*, 383 U.S. 1, 17 (1966)). The Federal Circuit has historically required that, in order to prove obviousness, the patent challenger must demonstrate, by clear and convincing evidence, that there is a "teaching, suggestion, or motivation to combine." The Supreme Court, however, rejected this "rigid approach" in *KSR Int'l Co. v. Teleflex Inc.*:

The obviousness analysis cannot be confined by a formalistic conception of the words teaching, suggestion, and motivation, or by overemphasis on the importance of published articles and the explicit content of issued patents. The diversity of inventive pursuits and of modern technology counsels against limiting the analysis in this way. In many fields it may be that there is little discussion of obvious techniques or combinations, and it often may be the case that market demand, rather than scientific literature, will drive design trends. Granting patent protection to an advance that would occur in the ordinary course without real innovation retards progress and may, in the case of patents combining previously known elements, deprive prior inventions of their value or utility.

KSR Int'l Co. v. Teleflex Inc., 500 U.S. 398, 402 (2007).

Since *KSR* was decided, the Federal Circuit has announced that, where a patent challenger contends that a patent is invalid for obviousness based on a combination of prior art references, "the burden falls on the patent challenger to show by clear and convincing evidence that a person of ordinary skill in the art would have had reason to attempt to make the composition or device, . . . and would have had a reasonable expectation of success in doing so." *PharmaStem Therapeutics, Inc. v. Viacell, Inc.*, 491 F.3d 1342, 1360 (Fed. Cir. 2007).

In addition to demonstrating that a reason exists to combine prior art references, the challenger must demonstrate that the combination of prior art references discloses all of the limitations of the claims. *Hearing Components, Inc. v. Shure Inc.*, 600 F.3d 1357, 1373-1374

(Fed. Cir. 2010) (upholding finding of non-obviousness based on the fact that there was substantial evidence that the asserted combination of references failed to disclose a claim limitation); *Velander v. Garner*, 348 F.3d 1359, 1363 (Fed. Cir. 2003) (explaining that a requirement for a finding of obviousness is that "all the elements of an invention are found in a combination of prior art references").

"Secondary considerations," also referred to as "objective indicia of non-obviousness," such as "commercial success, long felt but unsolved needs, failure of others, etc." may be used to understand the origin of the subject matter at issue, and may be relevant as indicia of obviousness or non-obviousness. Graham, 383 U.S. at 17-18. Secondary considerations may also include copying by others, prior art teaching away, and professional acclaim. See Perkin-Elmer Corp. v. Computervision Corp., 732 F.2d 888, 894 (Fed. Cir. 1984), cert. denied, 469 U.S. 857 (1984). Evidence of "secondary considerations," must be considered in evaluating the obviousness of a claimed invention, but the existence of such evidence does not control the obviousness determination. In order to accord objective evidence substantial weight, its proponent must establish a nexus between the evidence and the merits of the claimed invention, which is generally made out "when the patentee shows both that there is commercial success, and that the thing (product or method) that is commercially successful is the invention disclosed and claimed in the patent." In re GPAC Inc., 57 F.3d 1573, 1580 (Fed. Cir. 1995). But secondary considerations, such as commercial success, will not necessarily dislodge a determination of obviousness based on an analysis of the prior art. See KSR, 500 U.S. at 426 (commercial success did not alter conclusion of obviousness). A court must consider all of the evidence under the Graham factors before reaching a decision on obviousness. Richardson-Vicks,

122 F.3d at 1483-84.

The ID finds that claims 9 and 10 of the '455 patent are obvious in view of Gist combined with the knowledge of one of ordinary skill in the art and/or Kuboki. ID at 54. The ID also finds that the '455 patent is obvious in view of Kuboki in combination with the knowledge of one of ordinary skill in the art and/or Gist. ID at 58. The Commission did not review the ID's findings that the asserted claims are obvious in view of Gist combined with the knowledge of one of ordinary skill in the art. However, since our discussion concerning Kuboki involves analysis of this knowledge, we will briefly discuss the ID's findings on this issue.

With respect to the Gist reference, Respondents contended before the ALJ that "it would have been obvious to one of ordinary skill in the art to include the processor in the same IC package as the bus termination circuitry." ID at 46. Specifically, Respondent asserted that "at the time of the filing of the '455 patent, there was a long-standing, industry-wide trend toward integrating more and more functionality and circuitry onto a single chip," a point with which Respondents noted that Freescale's expert, Dr. Subramanian, agreed. *Id.* (citing Subramanian, Tr. at 656:2-7). Respondents further claimed that "microprocessors with on-chip bus termination circuits were already known in the art" and, thus, "a person or ordinary skill in the art would have considered it obvious to integrate the CPU and the dynamic termination circuitry of Gist." ID at 46-47.

The ALJ found that the testimony of both parties' experts show that "one of ordinary skill in the art at the time of the filing of the '455 patent would have found it obvious to integrate the processor and the bus termination circuitry of Gist on a single chip." ID at 49-50 (citing RX-1C at Q. 306, 309; Subramanian, Tr. at 656:2-7); see also id. at 52 (citing Subramanian, Tr. at

614:16-25, 617:4-8 (admitting that "[m]icroprocessors with on-chip bus termination circuits were [] known before the '455 patent[.]"). Specifically, the ALJ noted Dr. Knox' testimony regarding the benefits of single chip integration, namely "reduced size, reduced costs, reduced power consumption, and increased speed[,]" and that "one of ordinary skill in the art would have had a reasonable expectation of success in integrating the processor and bus termination circuitry of Gist on a single chip, as 'integration of multiple functionalities into a single integrated circuit was routinely practiced in the industry." ID at 50 (citing RX-1C at Q. 310, 312-15. The ALJ also credited Dr. Knox' reliance on an April 1992 IEEE article, concerning the trend towards chip integration, in finding that "one of ordinary skill in the art would be motivated to integrate the data processor and bus termination circuitry of Gist onto a single chip." *Id.* (citing RX-1C at Q. 149; RX-31 (IEEE article) at 52-53).

With respect to the teachings of the Kuboki reference, the ALJ noted that the parties disputed whether Kuboki discloses "[a] data processor within an integrated circuit package" that contains "a plurality of bus termination circuits," meaning a data processor and bus termination circuits on a single chip, and the limitation "a plurality of external pins" and "a plurality of bus termination circuits." ID at 41. Although he concluded that Kuboki does not anticipate claims 9 and 10 of the '455 patent, the ALJ found that Kuboki does explicitly disclose the limitation "a microprocessor with on-chip dynamic bus termination circuitry." *Id.*; *see also* ID at 51. Specifically, the ALJ noted that "Kuboki discloses nine differing embodiments of termination circuitry" as well as "a '[m]icroprocessor incorporating any one of the first through the ninth device as the input/output interface." ID at 41 (citing RX-5 (Kuboki) at ¶ 7-16, 39). The ALJ found that this language discloses "a single circuit including both a processor and termination

circuitry," crediting Dr. Knox's testimony that "since a microprocessor is itself an integrated circuit, the only logical reading is that Kuboki teaches a microprocessor with on-chip dynamic termination circuitry." *Id.* (citing RX-1C at Q. 376, 380).

The ALJ found that "[b]oth Kuboki and Gist are related to the same subject matter, namely dynamic bus termination circuitry . . . [t]hus, it would be natural for one of ordinary skill in the art to look to the teachings of Kuboki to modify the structure of Gist to integrate the processor and bus termination circuitry." *Id*. (citing RX-1C at Q. 457). The ALJ found that Freescale's argument that there were technological concerns that taught against single-chip integration "miss the mark" because "[t]he technical and/or financial problems [regarding] incorporating the claimed invention into a commercial product do not negate the fact that a prior art reference expressly discloses incorporating bus termination circuitry on a microprocessor." ID at 52.

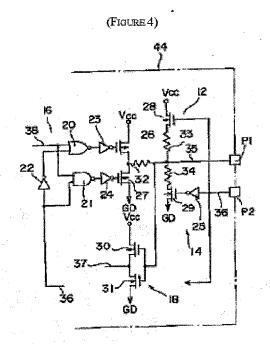

With respect to the obviousness of claim 9 in view of Kuboki, the ALJ found that, as for the missing element of Kuboki – "a plurality of external pins" and "a plurality of bus termination circuits" – Respondents' expert, Dr. Knox, opined that "[a] parallel data bus with multiple lines was a standard feature for high performance microprocessors in 1993[,]" such as the microprocessor disclosed by Kuboki, and that "use of a parallel data bus with multiple lines would require the use of a plurality of external pins, one for each data line." ID at 56-57 (citing RX-1C at Q. 410, 412). In particular, the ALJ noted Dr. Knox' testimony that "it would have

<sup>&</sup>lt;sup>3</sup> Although Freescale did not request review of the ALJ's findings concerning the limitations "a plurality of external pins" and "a plurality of bus termination circuits," we recite them here by way of background for our discussion below.

been a matter of routine design choice to replicate the bus termination circuitry shown in Figure 4 [of Kuboki] for each data line, thereby resulting in a plurality of bus termination circuits." *Id.* (citing RX-1C at Q. 413; *see also* Q. 416 (stating that "bus I/O interfaces are module, and are generally obtained by replicating a bus I/O cell for a single data line."). The ALJ further noted Dr. Knox' testimony that "Gist teaches the use of bus termination circuitry in the context of a parallel data bus." ID at 57 (citing RX-1C at Q. 453-454, 459-460). Dr. Knox opined that "one of ordinary skill in the art would have been motivated to make this modification of Kuboki because use of a parallel bus with multiple data lines increases the data transmission rate of the bus." *Id.* (citing RX-1C at Q. 417-418). The ALJ found that Freescale's expert, Dr. Subramanian, failed to rebut Dr. Knox's testimony. ID at 57-58 (citing CX-408 at Q. 151).<sup>4</sup>

Respondents similarly argued before the ALJ that "to the extent that Kuboki is determined not to disclose a processor and termination circuitry integrated onto one integrated circuit, it would have been obvious to one of ordinary skill in the art that the processor and termination circuitry of Kuboki could be integrated." ID at 54. Respondents further asserted that "to the extent that Kuboki is found to only disclose a single termination circuit for a single pin, it would have been obvious to one of ordinary skill in the art to implement the teachings of Kuboki in microprocessor technology using a parallel data bus and, thus, including multiple pins and multiple bus termination circuits . . . [or] to combine Kuboki and Gist to use the bus termination circuitry of Kuboki with the parallel bus of Gist." *Id.* The ALJ noted, however, that he explicitly found, in discussing anticipation, that "Kuboki clearly discloses the limitation '[a]

<sup>&</sup>lt;sup>4</sup> There was no dispute that either Gist or Kuboki discloses the additional limitations of claim 10 of the '455 patent. ID at 53-54, 58.

data processor within an integrated circuit package' with integrated bus termination circuitry."

ID at 56.5

Although we agree with the ALJ that Kuboki in combination with the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent, we do so for different reasons than those discussed in the ID. In particular, while we agree that the claim limitations "a plurality of external pins" and "a plurality of bus termination circuits" would have been obvious in light of the knowledge of one of ordinary skill in the art (*see* ID at 56-58), we find that the Kuboki reference does not disclose the claim limitation "[a] data processor within an integrated circuit package comprising: . . . a plurality of bus termination circuits."

The relevant passages of Kuboki are as follows:

Microprocessor incorporating the semiconductor integrated circuit device set forth in any of claims 1 through 9 as the input/output interface.

RX-5 at Claim 10 (emphasis added);

Microcomputer incorporating the semiconductor integrated circuit device set forth in any of claims 1 through 9 as the input/output interface.

RX-5 at Claim 11 (emphasis added);

(FIELD OF INDUSTRIAL APPLICATION) This invention relates to a semiconductor integrated circuit device, particularly to a semiconductor integrated circuit device ideally suited to measuring the impedance matching between input/output interfaces when transmitting signals via input/output interfaces, and to a microprocessor and microcomputer that uses this device.

RX-5 at  $\P$  1 (emphasis added);

<sup>&</sup>lt;sup>5</sup> The Commission did not review the ID's findings concerning secondary considerations. *See* ID at 60-62; Notice of Review In Part at 3.

*Microprocessor incorporating* any one of the first through the ninth device as the input/output interface.

RX-5 at  $\P$  16 (emphasis added);

Microcomputer incorporating any one of the first through the ninth device as the input/output interface.

RX-5 at ¶ 17 (emphasis added);

Although semiconductor integrated circuit devices were described in each of the aforesaid embodiments, the same effect as the aforesaid embodiments can be obtained by *using these devices to constitute a microprocessor or microcomputer*.

RX-5 at ¶ 39. The ID finds that this language provides an "unambiguous disclosure of a microprocessor with on-chip dynamic bus termination circuitry." ID at 51 (citing RX-5 (Kuboki); RX-1C at Q. 376, 380). The evidence shows, however, that the issue is not as straightforward as might appear at first glance.

The dispute concerns Kuboki's use of both the terms "microprocessor," which may refer to a single chip, and "microcomputer," which by definition is almost never incorporated on a single chip because it encompasses the many devices necessary for the microcomputer to operate. See CX-408C (Subramanian Rebuttal Witness Statement ("RWS")) at Q. 126. We note, however, that the relevant portion of Kuboki is not the disclosure concerning a "microcomputer." Rather, it is the disclosure concerning a "microprocessor." Kuboki teaches a "microprocessor" that not only "uses" the disclosed bus termination circuitry (see RX-5 at ¶ 1) but "incorporates" (see RX-5 at Claim 10, ¶ 16) the circuitry and that the circuitry is used to "constitute" a "microprocessor" (see RX-5 at ¶ 39). While the use of the term "incorporate" and "constitute" in the context of a multi-chip device like a microcomputer may mean that the bus termination circuitry is one of the many chips used to make up the microcomputer, it does not need to have

that same meaning in reference to a single device.

This understanding, however, does not resolve the question. In particular, Freescale's expert, Dr. Subramanian, acknowledged that a microprocessor need not, in fact, be implemented on a single chip or, in the language of claim 9 of the '455 patent, "within an integrated circuit package." Specifically, he testified as follows:

As I discussed earlier, there is absolutely no necessity that all microprocessor functionality be incorporated within a single package, and indeed, even today, structures such as de-coupling capacitors, etc., are routinely placed off-chip and outside the package.

CX-408C at Q. 126. As such, while the language of Kuboki strongly suggests the incorporation of a microprocessor and bus termination circuitry into a single package, too much ambiguity remains to allow us to find that Kuboki necessarily discloses a single integrated circuit that includes both a processor and termination circuitry. As such, we find that Kuboki does not disclose by clear and convincing evidence the "[a] data processor within an integrated circuit package comprising: . . . a plurality of bus termination circuits" limitation of claim 9 of the '455 patent.

Although we find that Kuboki does not sufficiently disclose the limitation "[a] data processor within an integrated circuit package comprising: . . . a plurality of bus termination circuits" of claim 9, we adopted without review the ID's finding that it would have been obvious to one of ordinary skill in the art to integrate a data processor with bus termination circuitry on the same chip. *See* ID at 49-50; Notice of Review In Part at 3. As such, we find that Kuboki in combination with the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent with respect to the limitation "[a] data processor within an integrated circuit

package comprising: . . . a plurality of bus termination circuits" of claim 9. Moreover, because, as the ID finds, Gist discloses the limitations "a plurality of external pins" and "a plurality of bus termination circuits" (ID at 57), we also find that Kuboki in combination with Gist and the knowledge of one of ordinary skill in the art renders obvious claims 9 and 10 of the '455 patent.

#### B. Infringement

Unfair acts under section 337 include "all forms of infringement, including direct, contributory, and induced infringement." Certain Home Vacuum Packaging Machines, Inv. No. 337-TA-496, Order No. 44, 2004 ITC LEXIS 202 \* 2, n.2 (Mar. 3, 2004). To establish infringement, there must be a preponderance of evidence. See Creative Compounds, 651 F.3d at 1314. A determination of patent infringement encompasses a two-step analysis. Advanced Cardiovascular Sys., Inc. v. Scimed Life Sys., Inc., 261 F.3d 1329, 1336 (Fed. Cir. 2001) ("Scimed"). First, the court determines the scope and meaning of the patent claims asserted, and then the properly construed claims are compared to the allegedly infringing device. *Id.* "Literal infringement of a claim exists when each of the claim limitations reads on, or in other words is found in, the accused device." Allen Eng. Corp. v. Bartell Indus., 299 F.3d 1336, 1345 (Fed. Cir. 2002). Direct infringement includes the making, using, selling, offering for sale and importing into the United States an infringing product, without authority. 35 U.S.C. § 271(a). To prove direct infringement, the plaintiff must establish by a preponderance of the evidence that one or more claims of the patent read on the accused device either literally or under the doctrine of equivalents ("DOE"). Scimed, 261 F.3d at 1336.

Under DOE, "a product or process that does not literally infringe upon the express terms of a patent claim may nonetheless be found to infringe if there is equivalence between the

elements of the accused product or process and the claimed elements of the patented invention." Warner-Jenkinson Co. v. Hilton Davis Chem. Co., 520 U.S. 17, 21 (1997). Equivalency may be determined using the "triple identity test" and thus "focusing on the function served by a particular claim element, the way that element serves that function, and the result . . . obtained by that element. . . ." Id. at 39. Regardless of the linguistic framework of the test used, the "essential inquiry" is: "[d]oes the accused product or process contain elements identical or equivalent to each claimed element of the patented invention?" Id. at 40.

Freescale argued before the ALJ that "each of the [Accused] Zoran Hybrid Termination

Products [ ] ID at 112.

(citing RX-218C (Herzen RWS) at Q. 97; RX-219C (Auld RWS) at Q. 111; CX-194C at 1; CX-276C at 1; CX-401C (Subramanian Direct Witness Statement) at Q. 211-14; JX-30C; JX-53C).

Freescale asserted that "[

], as shown in JX-30C at ZCO 1047 and JX-53C at ZCO 1269." ID at 115 (citing CX-401C at Q.246-47). Freescale further asserted that "the termination circuitry in the bus termination circuit [

J." *Id.* (citing JX-7C (Auld Dep.) at 68:20-69:5; JX-30C at ZCO 1048; JX-53C at ZCO 1272; JX-7C at 68:20-69:5). Freescale further asserted that "[

]." ID at 118-119 (citing JX-7C at 76:18-78:9; CX-401C at Q. 227-28; JX-30C at ZCO 1048; JX-53C at ZCO 1272; see CDX-4C.13 (Group II) and CDX-4C.20 (Group III) - annotated schematics of [

1.

With respect to the limitation "a conductor coupled to each input of the bus termination circuits in the plurality of bus termination circuits, the conductor providing the control signal, wherein the control signal, when asserted, allows each bus termination circuit in the plurality of bus termination circuits to couple at least one circuit component to the bus to reduce signal reflection on the bus, the control signal, when deasserted, allows each bus termination circuit in the plurality of bus termination circuits to decouple at least one circuit component from the bus," Freescale accused "[

]" as the claimed "conductors." ID at 118

(citing CX-401C at Q. 227, 251.) Freescale claimed that "[

]." *Id.* (citing Auld, Tr. at 180:15-183:10; JX-7C at 71:12-72:8, 74:13-76:13).

Freescale asserted that "[

]." ID at 115-116. Freescale argued, therefore, that "[

]." ID at 116 (citing

CX-401C at Q. 222, 246). Freescale further asserted that "in addition to [

][which] set the amount of termination impedance. *Id*.

(citing JX-7C at 73:8-24, 76:18-78:9). Freescale asserted that the accused "control signals, when

asserted, couple at least one circuit component, a transistor and one or more resistors, to the bus through the [ ]." ID at 118 (citing Auld,

Tr. at 180:15-183:10; JX-30C at ZCO 1048). Freescale further asserted that "when these control signals are deasserted, these circuit components are decoupled from the bus." *Id*.

The ID finds that Motorola failed to show by a preponderance of the evidence that the Accused Zoran Hybrid Termination Products satisfy the "control signal, when asserted . . . when deasserted" limitation of claim 9 of the '455 patent. ID at 143.6 Although the ALJ apparently agreed that [ ] in JX-30C and JX-53C is a "bus termination circuit," he found, with respect to the limitation at issue, that Freescale failed to "sufficiently link the assertion or deassertion of the accused control signals [ ] with the coupling or decoupling of circuit components to say that one 'allows' the other." ID at 154 (emphasis in original). Specifically, the ALJ found that, while "[t]he accused bus termination circuit receives [the accused control signals] as input signals[,]" the [

] respectively. ID at 154-155 (citing JX-30C at ZCO 1047, 1048; JX-53C at ZCO 1262, 1272). The ALJ noted Freescale's reliance on Zoran's witness, Mr. Auld, to show a link between the [

]. ID at 155. In particular, Freescale cited Mr.

Auld's testimony that "[

<sup>&</sup>lt;sup>6</sup> The ALJ noted that Zoran and Freescale agree that all of the Accused Zoran Hybrid Termination Products share the same interface circuitry and may be treated together for purposes of the infringement analysis. ID at 144.

]." *Id.* (emphasis in original) (citing Auld, Tr. at 181:5-182:8; JX-7C (Auld Dep.) at 73:17-24). The ALJ found, however, that Freescale's argument that "a signal used 'in combination with other signals,' or a signal that contributes 'in part,' to coupling circuitry" is insufficient to satisfy the disputed claim limitation. *Id.* The ALJ found that "Freescale imposes no limits on how insignificant the contributed 'part' can be, or how many other signals can be used in combination with the alleged 'control signal,' and still meet this limitation." *Id.* The ALJ stated that "[a] plain and ordinary reading of [the term] 'allows' [in claim 9] does not permit such an attenuated relationship between the accused control signal and whether circuitry is coupled to or decoupled from the bus." *Id.* The ALJ also found that "nothing in the intrinsic record supports Freescale's position[.]" *Id.*

We agree with the ALJ that the evidence does support by a preponderance of the evidence a conclusion that that accused signals [ ] signals satisfy the limitation the "control signal, when asserted . . . when deasserted" limitation of claim 9 of the '455 patent. We find, however, that the ALJ's finding is supported for reasons in addition to those articulated in the ID.

The Accused Zoran Hybrid Termination Products are shown in exhibits JX-30C (Group III) and JX-53C (Group III). <sup>7</sup> Freescale accuses block [ ] as the "bus termination circuit" of claim 9 of the '455 patent. ID at 115. Specifically, block [

<sup>&</sup>lt;sup>7</sup> The parties agree that the Group II and Group III products operate similarly. ID at 102. As such, we will refer to the schematics that are clearest from either Group II or Group III.

]. Id. The arrangement of components in block is shown in the schematics JX-30C at ZCO 1047 (Group II) and JX-53C at ZCO 1269 ] is shown in the s schematics JX-30C at ZCO 1048 (Group (Group III. The [ II) and JX-53C at ZCO 1272 (Group III) as follows: E ] RDX-10-14C (showing JX-30C at ZCO 1048). Zoran corporate witness, Mr. Auld, testified at his deposition that the unasserted signal ] in the Accused [

Zoran Hybrid Termination Products.<sup>8</sup> JX-7C (Auld Dep.) at 114:20-115:2. He explained that the [

]." *Id.* at 161:11-23.

So, while the accused signals [

](see JX-7C at 72:3-8) and the accused signals

[

](see JX-7C at 71:18-23), without the signal [

] would not know whether it was in input mode or termination mode in the first place. As a result, without assertion of the [

] – will not signal to the termination

circuits that they should turn on.

We, therefore, affirm the ID's finding that Freescale has failed to show that the Accused Zoran Hybrid Termination Circuits infringe claims 9 and 10 of the '455 patent for both the reasons stated in the ID and for the additional reasons discussed above.

#### C. Domestic Industry: Economic Prong

Sections 337(a)(2) and (3) set forth the domestic industry requirement:

- (2) Subparagraphs (B), (C), (D), and (E) of paragraph (1) apply only if an industry in the United States, relating to the articles protected by the patent, copyright, trademark, mask work, or design concerned, exists or is in the process of being established.

- (3) For purposes of paragraph (2), an industry in the United States shall be considered to exist if there is in the United States, with respect to the articles protected by the patent, copyright, trademark, mask work, or design concerned—

<sup>&</sup>lt;sup>8</sup> The signal is shown, for example, in exhibit JC-53C at 1272 at near the bottom left of the figure.

- (A) significant investment in plant and equipment;

- (B) significant employment of labor or capital; or

- **(C)** substantial investment in its exploitation, including engineering, research and development, or licensing.

19 U.S.C. §§ 1337(a)(2) and (3).

The economic prong of the domestic industry requirement is satisfied by meeting the criteria of any one of the three factors listed in sections 337(a)(3) above. When a complainant seeks to satisfy the domestic industry requirement through its investments in licensing under section 337(a)(3)(C), the complainant must show that it has made a substantial investment in the exploitation of the asserted patent through licensing. 19 U.S.C. § 1337(a)(3)(C); Certain Multimedia Display and Navigation Devices and Systems, Components Thereof, and Prods. Containing Same, Inv. No. 337-TA-694, Comm'n Op. at 7-8 (Aug. 8, 2011) ("Navigation Devices"). In order for a particular activity to be considered "exploitation" through licensing within the meaning of the statute, the complainant must demonstrate that it: (1) relates to the asserted patent; (2) relates to licensing; and (3) occurred in the United States. Navigation Devices, Comm'n Op. at 7-8.

Activities that meet these three requirements merit consideration in the Commission's evaluation of whether a complainant has satisfied the domestic industry requirement, but the inquiry does not end there. *Id.* Complainant must also demonstrate the extent of its investment in these activities. In the portfolio licensing context, the Commission has indicated that it

<sup>&</sup>lt;sup>9</sup> Because the statute requires that investment activities satisfy all three of these requirements, the absence of any one of them will defeat complainant's attempt to rely on that activity to satisfy the domestic industry requirement. *Navigation Devices*, Comm'n Op. at 15 n.12.

considers the relative importance of the asserted patent to the licensing investment to determine to what extent the investment in the entire portfolio can be attributed to the asserted patent.

Navigation Devices, Comm'n Op. at 8 ("Because Pioneer's activities are associated both with the asserted patents and unasserted patents, a key issue presented is the strength of the nexus between the activities and the asserted patents.").

Finally, complainant must establish that its investment in licensing the asserted patent is substantial. *Id.* The Commission has indicated that whether an investment is "substantial" may depend on:

- (1) the nature of the industry and the resources of the complainant;

- (2) the existence of other types of "exploitation" activities;

- (3) the existence of license-related "ancillary" activities;

- (4) whether complainant's licensing activities are continuing; and

- (5) whether complainant's licensing activities are the type of activities that are referenced favorably in the legislative history of section 337(a)(3)(C).

*Id.* at 15-16. The complainant's return on its licensing investment (or lack thereof) may also be circumstantial evidence of substantiality. *Id.* at 16.

Before the ALJ, Freescale relied on its "[

J." ID at 158 (citing CX-402C (Chastain WS) at Q. 11).

Freescale further relied on the fact that it "[

]," with related salary

expenses totaling approximately [

]. ID at 158-159

(citing CX-402C at Q. 13-18, 22; CX-1C (Chastain Decl.) at ¶¶ 4-5). Freescale also noted that its "[

]." ID at 159 (citing CX-402C at Q. 24-25; CX-1C at ¶ 3).

Freescale contended that "all of these costs were related to employees and licensing efforts in the United States." *Id.* Freescale further relied on non-payroll investments of approximately

]. ID at 173 (citing CX-402C at Q. 24-25; CX-1C at Tab

A). Freescale asserted that ""[

ſ

]." *Id.* (citing CX-402C at Q. 27).

Freescale contended that it "granted licenses to the '455 patent [ ]" and that "[ ]." *Id.* (citing CX-402C at Q.37-41, 51-63; CX-1C at ¶¶ 6-7; JX-26C [ ]; CX-29C [

]). Freescale claimed that it often [ ] and that "[

]." Id. (citing CX-402C at Q. 58-61, 81

]. Freescale further noted

that the Commission declined to review the finding on summary determination in *Integrated Circuits I* that Freescale made a substantial investment in licensing with respect to the '455 patent. *Id.* (citing CX-2C (*Integrated Circuits I*, Order No. 33); CX-3 (Commission Notice of non-review)).

Respondents argued before the ALJ that "Freescale failed to offer any evidence on any of the five factors relating to the nexus between the claimed investment and the '455 patent" that

the Commission noted in *Navigation Devices*. ID at 160 (citing Order No. 19 (denying Freescale's motion for summary determination that it satisfies the domestic industry requirement based on licensing). Specifically, Respondents asserted that Freescale conceded that it licenses the '455 patent [

]. Id. Respondents further asserted that "[

]" and uses its patent portfolio [

]. ID at 160-161.

Respondents also asserted that Freescale has not offered any evidence "[

]" or "[

]." ID at 161.

The IA also argued before the ALJ that Freescale failed to satisfy the domestic industry requirement based on its licensing activities. ID at 162. In addition to the arguments presented by Respondents, the IA asserted that "[

]." Id. The IA further argued that "[

]." Id. The IA also contended that "[

]." *Id*.

The ID finds that Freescale failed to demonstrate that it satisfies the domestic industry requirement for the '455 patent based on its licensing activities. ID at 163. The ALJ did find that Freescale has demonstrated a nexus between its licensing activities in general and the '455

patent. ID at 163-168. The ALJ also found, however, that "Freescale has not met its burden to demonstrate that it has made a 'substantial investment' in licensing as required by 19 U.S.C. § 1337(a)(3)(C)." ID at 176.

The ALJ noted that, for the employees that Freescale identifies as being involved in licensing operations, Freescale's corporate witness, "Mr. Chastain[,] acknowledges that [

]."

ID at 171 (citing JX-16C (Chastain Dep.) at 123:4-20). The ALJ, therefore, found that "it is improper to include the employees' full salaries in the calculation when [

]." ID at 171-172. The ALJ also declined to consider Freescale's non-payroll investments, specifically, those concerning its [

]." ID at 173 (citing JX-16C at 179:4-180:8, 225:25-226:15; CX-402C at Q. 27; JX-23C (Guzaldo Dep.) at 62:22-63:7). The ALJ found that "[

]." ID at 174.

The ALJ, therefore, considered only Freescale's remaining non-payroll expenses, which amounted to [ ]. ID at 175. The ALJ found that "Freescale is a large corporation with [

]." Id. (citing RX-156 at 5, 35). The ALJ concluded that "[

]" and is, therefore, not substantial

within the meaning of section 337(a)(3)(C). *Id* (citing *Navigation Devices* at 15 (finding that "whether an investment is substantial may depend on the industry and the size of the complainant.")

The dispute with respect to whether Freescale has demonstrated that it has a license-based domestic industry centers on the issue of how to apportion their investments in licensing. The Commission has recently provided guidance on this issue in Certain *Semiconductor Chips* and *Products Containing Same*, Inv. No. 337-TA-753, Comm'n Op. at 44-51 (July 31, 2012) ("*Semiconductor Chips*"). In that case, the complainant, Rambus, Inc., asserted two groups of patent claims, the Barth patents and the Dally patents. *Id.* at 4-5. Rambus argued that it had a licensed-based domestic industry due to its investment in licensing the Barth and Dally patents. *Id.* at 44. The presiding ALJ in that investigation found that Rambus had shown that its

investment in licensing those patents was "substantial," but the Commission reversed the ALJ's determination. *Id.* In reaching the decision, the Commission assumed for purposes of its analysis that Rambus had demonstrated a nexus between the asserted patents and Rambus's license portfolios. The Commission noted, however, that "what is wanting in this investigation . . . is evidence specifically demonstrating [the] investment made in the licenses upon which Rambus relies, as opposed to overall firmwide licensing expenses." *Id.* at 47, n. 19. The Commission, therefore, concluded that the evidence Rambus presented concerning its

total amount of licensing expenditures and total number of licensing-related employees . . . does not allow the Commission to qualitatively or quantitatively determine what portion of [Rambus's firmwide investment], or what portion of the expenses associated with the activities of . . . Rambus employees that work on the overall licensing program, could be allocated in some fashion to licensing the Dally and Barth patents.

*Id.* at 47.

Similar to the evidence Rambus presented in *Semiconductor Chips*, the evidence presented by Freescale here does not allow the Commission to ascertain how the '455 patent relates to its overall licensing program. Freescale offers [

]. JX16C at 58:9-11; 59:10-60:16. Freescale does not indicate the number of portfolio licenses it has entered into that actually license the '455 patent.

Instead, Freescale simply put into evidence a sampling of its [

]. CX-402C at Q. 40-42. Further, Freescale's corporate witness, Mr. Chastain, did not clarify the issue. He did testify that the company has

]. JX-16C

at 22:11-17, 27:11-20. Mr. Chastain stated, however, that he was unaware of what percentage

[ ] related to the various technology areas, although he speculated that the circuit design area, of which the '455 patent is a part, [

]. *Id.* at 27:21-29:19. Although Mr. Chastain estimated that Freescale has entered into [ ], he could not detail what percentage of

Freescale's licensing revenues since 2005 are attributable [

]. *Id*.

Based on this evidence, we are left to speculate as to what percentage of Freescale's licensing investment is attributable to those licenses that include the '455 patent. Although the Commission does not require mathematical precision, it does require an adequate evidentiary basis for evaluating the level of investment for the licenses that include the '455 patent. As such, even assuming that the ID's finding of a nexus between Freescale's licensing portfolios and the '455 patents is correct, Freescale has failed to present sufficient evidence to allow us to determine what portion of its investment we should consider, and thus, to determine whether its investment is "substantial," as required by section 337(a)(3)(C).

Furthermore, although not addressed by the ALJ, we note that the payroll evidence Freescale presents is from 2011 and 2012, and thus, mostly from a time period subsequent to the filing of the Complaint in June of 2011. As the Commission noted in *Certain Video Game Systems and Controllers*, Inv. No. 337-TA-743, Commission Opinion at 4-7 (January 20, 2012) (Public Version), although there may be circumstances in which it is appropriate to look at a complainant's domestic activity subsequent to the filing of the Complaint, "as a general matter,

the only activities that are relevant to the determination of whether a domestic industry exists or is in the process of being established are those that occurred before the complaint was filed." Id. at 5. There is no evidence in this investigation that it is appropriate to look at Freescale's postcomplaint activities. For instance, Freescale has not filed for bankruptcy since filing its Complaint, neither has any "new, relevant and timely disclosed evidence" come to light, nor does Freescale's industry appear to be "dwindling." See, e.g., Certain Semiconductor Integrated Circuits and Products Containing the Same, Inv. No. 337-TA-665, ID at 229-30 (Oct. 19, 2009) (examining a complainant's domestic industry where the complainant filed for bankruptcy after filing a complaint with the Commission) (unreviewed in relevant part); Certain Electronic Devices, Including Mobile Phones, Portable Music Players, and Computers, Inv. No. 337-TA-701, Order No. 58, at 6 (Nov. 18, 2010) (unreviewed) ("the International Trade Commission typically looks to the time a complaint is filed, but there have been a number of instances when it has been acceptable to look later in the investigation, either because of the development of new, relevant and timely disclosed evidence or because there is evidence that a complainant's domestic industry is dwindling."); Certain Electronic Imaging Devices, Inv. No. 337-TA-726, Order No. 18 (Feb. 7, 2011) (unreviewed) ("The Commission . . . has examined the existence of a domestic industry at various points in the investigation time line, depending on the circumstances of the case."). We further note that Freescale was formed in 2004, and that in Integrated Circuits I, Freescale provided information concerning its domestic industry in 2009 and 2010, which information was readily available to Freescale in this investigation. See CX-2C (Integrated Circuits I, Order No. 33). As such, we believe it is inappropriate for Freescale to rely primarily on post-complaint activity in attempting to establish its domestic industry in this

investigation.

With respect to Freescale's non-payroll costs, an analysis of these investments suffers from the same evidentiary problems as its payroll investments. Specifically, there is no evidence showing what portion of Freescale's non-payroll licensing investments have a nexus to the '455 patent. Moreover, we cannot even determine from the evidence Freescale presents what portion of its licensing investments concerns domestic versus foreign licenses. As such, we have no way to determine the amount of Freescale's investments we should consider in determining whether or not its domestic investments are substantial within the meaning of the statute.

We do recognize that Freescale has been rather successful in licensing companies in the semiconductor and electronic device industry. *See* CX-1C at Tab D (listing [

] as licensees to Freescale's portfolio that includes the '455 patent). It is difficult, however, to determine how Freescale's revenues support its claims of a domestic industry because it admits that the licenses are [

]. See JX-16C at 29:11-19, 47:14-21, 59:7-15, 84:1-7. Contrast this with the facts in Certain Liquid Cristal Display Devices, Including Monitors, Televisions, and Modules and Components Thereof, Inv. No. 337-TA-741/749, Comm'n Op. (July 6, 2012), where the Commission found that the complainant licenses its patents in discrete technology groups. *Id.* at 117-119. Freescale does not provide any such level of detail, leaving us unable to determine how much of its licensing-based revenue to credit to those licenses that are related to the '455 patent. We, therefore, find that the question of whether Freescale's investment is substantial

cannot be analyzed due to a lack of an adequate evidentiary basis.

Freescale argued in its petition for review that the ID's finding of no domestic industry is contrary to the finding of the presiding ALJ in Integrated Circuits I. We note, however, that Freescale's motion for summary determination of a license-based domestic industry in Integrated Circuits I (Order No. 33, unreviewed) was granted prior to the issuance of the Commission's opinion in Navigation Devices. The Commission's opinion in Navigation Devices laid out a comprehensive framework which was not available to former Chief Judge Luckern in Integrated Circuits I. As the ALJ noted in denying Freescale's motion for summary judgment in this investigation, the decision in *Integrated Circuits I* did not analyze the factors that the ALJ was required to consider under Navigation Devices. See Order No. 19 at 7. Moreover, we note that, while Freescale is correct that the Navigation Devices opinion cites Order No. 33 in Integrated Circuits I approvingly, the citation was in the context of how a complainant may show a nexus between its licensing activities and the asserted patent, not whether or not the Commission should fully credit payroll expenses under a "substantial investment" analysis. See Navigation Devices at 11, n. 7 (citing Integrated Circuits I, Order No. 33 as "noting that the patent-at-issue was identified to potential licensees).

Accordingly, we affirm the ID's finding that Freescale failed to establish the existence of a domestic industry based on its licensing activities with the modified analysis indicated above.

#### IV. CONCLUSION

For the reasons discussed above, the Commission affirms with the above modifications the ID's finding of no violation of section 337.

By order of the Commission.

193

Lisa R. Barton Acting Secretary to the Commission

Issued: October 10, 2012

# CERTAIN INTEGRATED CIRCUITS, CHIPSETS, AND PRODUCTS CONTAINING SAME INCLUDING TELEVISIONS

337-TA-786

#### **CERTIFICATE OF SERVICE**

I, Lisa R. Barton, hereby certify that the attached **COMMISSION OPINION** has been served by hand upon Commission Investigative Attorney **Juan S. Cockburn** and the following parties as indicated, on **October 10, 2012**

Lisa R. Barton, Acting Secretary U.S. International Trade Commission 500 E Street, SW Washington, DC 20436

( ) Via Hand Delivery

## On Behalf of Complainant Freescale Semiconductor, Inc.:

Michael Chibib, Esq.

| BRACEWELL & GIULIANI LLP                               | (x) Via Overnight Mail   |

|--------------------------------------------------------|--------------------------|

| 111 Congress Avenue, Suite 2300                        | ( ) Via First Class Mail |

| Austin, TX 78701-4601                                  | ( ) Other:               |

| On Behalf of Respondents Funai Electric Co., Ltd       | <u>i.</u>                |

| and Funai Corporation, Inc.:                           |                          |

| Paul Devinsky, Esq.                                    | ( ) Via Hand Delivery    |

| MCDERMOTT WILL & EMERY LLP                             | (X) Via Overnight Mail   |

| 600 13 <sup>th</sup> Street NW, 12 <sup>th</sup> Floor | ( ) Via First Class Mail |

| Washington, DC 20005-3096                              | ( ) Other:               |

| On Behalf of Respondent MediaTek, Inc.:                |                          |

| Michael D. Esch, Esq.                                  |                          |

| WILMER CUTLER PICKERING                                | ( ) Via Hand Delivery    |

| HALE & DORR LLP                                        | (⋈ Via Overnight Mail    |

| 1875 Pennsylvania Ave., N.W.                           | ( ) Via First Class Mail |

| Washington, DC 20006                                   | ( ) Other:               |

## On Behalf of Respondent Zoran Corporation:

| Mark D. Fowler, Esq.     | ( ) Via Hand Delivery    |

|--------------------------|--------------------------|

| DLA PIPER LLP (US)       | (x) Via Overnight Mail   |

| 2000 University Avenue   | ( ) Via First Class Mail |

| East Palo Alto, CA 94303 | ( ) Other:               |

## UNITED STATES INTERNATIONAL TRADE COMMISSION Washington, D.C.

In the Matter of

CERTAIN INTEGRATED CIRCUITS, CHIPSETS, & PRODUCTS CONTAINING SAME INCLUDING TELEVISIONS Inv. No. 337-TA-786

## INITIAL DETERMINATION ON VIOLATION OF SECTION 337 AND RECOMMENDED DETERMINATION ON REMEDY AND BOND

Administrative Law Judge Robert K. Rogers, Jr.

(July 12, 2012)

#### Appearances:

#### For Complainant Freescale Semiconductor, Inc.:

Alan D. Albright, Esq.; Barry Shelton, Esq.; Michael Chibib, Esq.; Brian Nash, Esq. of Bracewell & Guiliani LLP, Austin, Texas

#### For Respondent MediaTek Inc.:

Keith L. Slenkovich, Esq.; Joseph F. Haag, Esq.; Nathan Walker, Esq.; Tobias Mock, Esq. of Wilmer Cutler Pickering Hale & Dorr LLP, Palo Alto, California

James M. Dowd, Esq. of Wilmer Cutler Pickering Hale & Dorr LLP, Los Angeles, California

T. Spence Chubb, Esq.; Michael D. Esch, Esq. of Wilmer Cutler Pickering Hale & Dorr LLP, Washington, DC

William F. Lee, Esq. of Wilmer Cutler Pickering Hale & Dorr LLP, Boston, Massachusetts

#### For Respondent Zoran Corporation:

Mark D. Fowler, Esq.; Timothy Lohse, Esq.; Michael G. Schwartz, Esq.; Erik Fuehrer, Esq.; Summer Krause, Esq. of DLA Piper LLP (US), East Palo Alto, California

## For the Commission Investigative Staff:

Lynn I. Levine, Esq., Director; Anne M. Goalwin, Esq., Supervisory Attorney; Juan Cockburn, Esq., Investigative Attorney; of the Office of Unfair Import Investigations, U.S. International Trade Commission, of Washington, DC

## TABLE OF CONTENTS

|           | ACKGROUND                                                            |             |

|-----------|----------------------------------------------------------------------|-------------|

| <b>A.</b> |                                                                      |             |

| В.        |                                                                      |             |

| 1         |                                                                      |             |

| 2         |                                                                      |             |

| 3         |                                                                      |             |

| C.        | Overview Of The Patent At Issue                                      |             |

| D.        | Products At Issue                                                    |             |

| II. J     | URISDICTION                                                          |             |

| A.        | Subject Matter Jurisdiction                                          | 4           |

| В.        | Personal Jurisdiction                                                | 4           |

| C.        | In Rem Jurisdiction                                                  | 4           |

| III.      | CLAIM CONSTRUCTION                                                   |             |

| A.        | Applicable Law                                                       | 5           |

| В.        | The '455 patent                                                      | 7           |

| 1         | . Level of Ordinary Skill in the Art                                 | 7           |

| 2         | . Agreed-Upon Constructions                                          | 8           |

| 3         | 6. "A Conductor Coupled to Each Input of Each of the Bus Termination | Circuits in |

| , t       | he Plurality of Bus Termination Circuits"                            | 8           |

| 4         | . "To Decouple At Least One Circuit Component From the Bus"          | 23          |

| IV.       | INVALIDITY                                                           | 27          |

| A.        | Applicable Law                                                       | 27          |

| 1         | Applicable Law                                                       | 28          |

| 2         | 2. Obviousness                                                       | 28          |

| В.        | Anticipation                                                         | 30          |

| 1         | . Gist                                                               | 30          |

| 2         | . Kuboki                                                             | 38          |

| C.        | Obviousness                                                          | 46          |

| 1         | . Gist In Combination With The Knowledge of One Of Ordinary Skill In | ı The Art   |

| 2         | ınd/or Kuboki                                                        |             |

| 2         | 2. Kuboki In Combination With The Knowledge of One Of Ordinary Ski   | ll In The   |

| A         | Art and/or Gist                                                      | 54          |

| 3         | 3. Secondary Considerations                                          | 58          |

| V. I      | SSUE PRECLUSION                                                      | 62          |

| VI.       | INFRINGEMENT                                                         | 71          |

| <b>A.</b> | Applicable Law                                                       | 71          |

| В.        | MediaTek                                                             | 72          |

| C.        | Zoran                                                                | 101         |

| VII.      | DOMESTIC INDUSTRY                                                    | 156         |

| A.        | Applicable Law                                                       | 156         |

| В.        | Analysis                                                             | 158         |

| VIII.     | REMEDY & BONDING                                                     |             |

| A.        | Limited Exclusion Order                                              | 177         |

| R         | Cossa & Dasist Ordan                                                 | 179         |

|    | . Bonding             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 180 |

|----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | MATTERS NOT DISCUSSED | The state of the s |     |